Lug structure and making method thereof

A technology of bumps and elastic layers, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

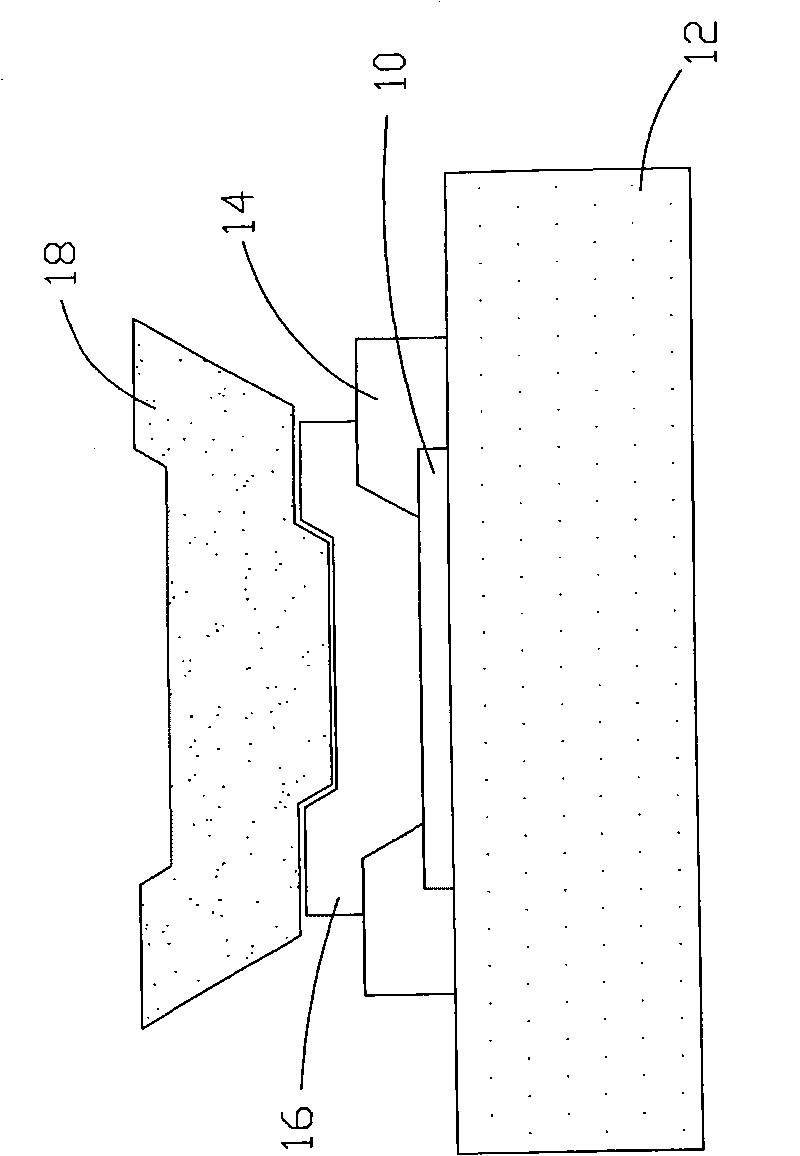

[0041] The main spirit of the smart bump structure of the first embodiment of the present invention is based on the smart structure design of the prior art. In order to cope with the continuous development of ICs with fine pitches, the pitch of IC bumps with fine pitches needs to be lower than 20μm, and the development and etching limit of the elastic layer spacing is 20μm, providing a new smart bump structure allows the bumping house to have more margins and successfully form a smart bump structure.

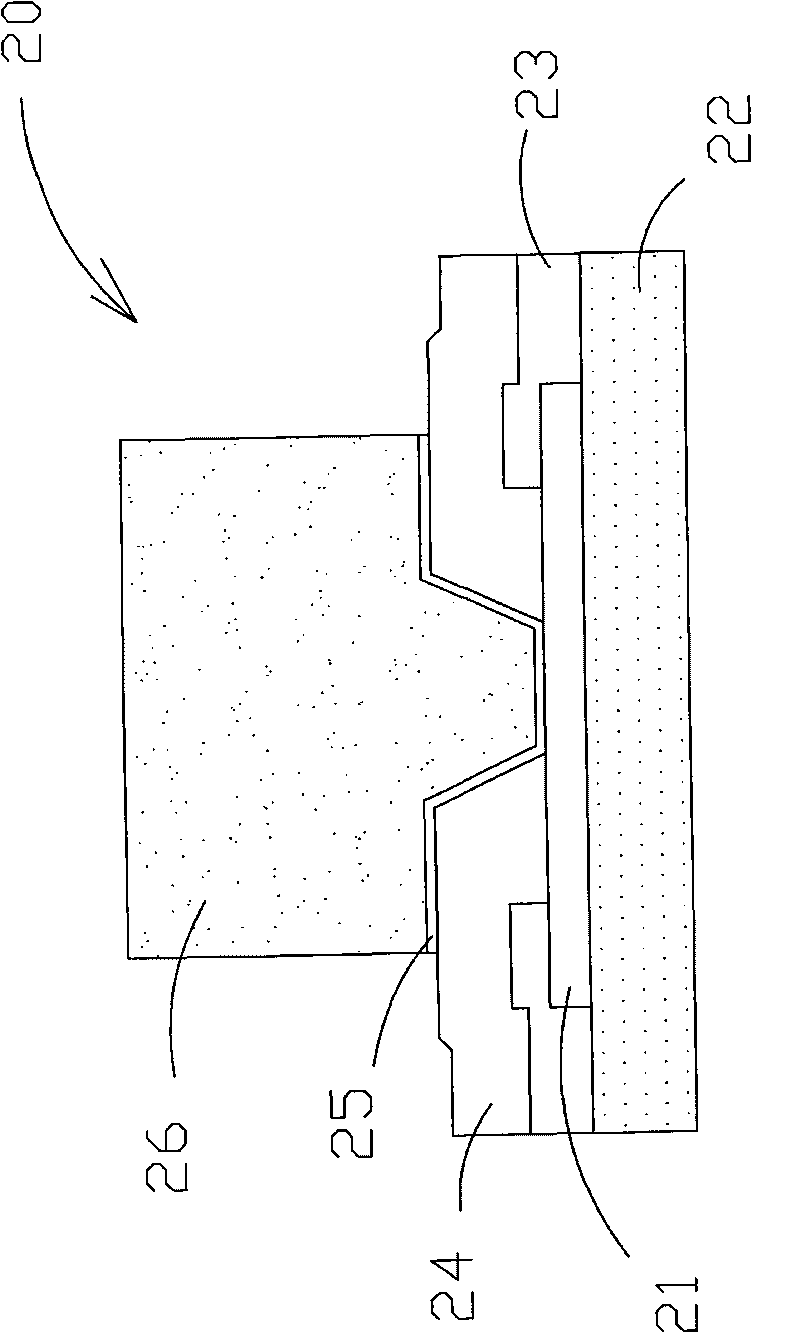

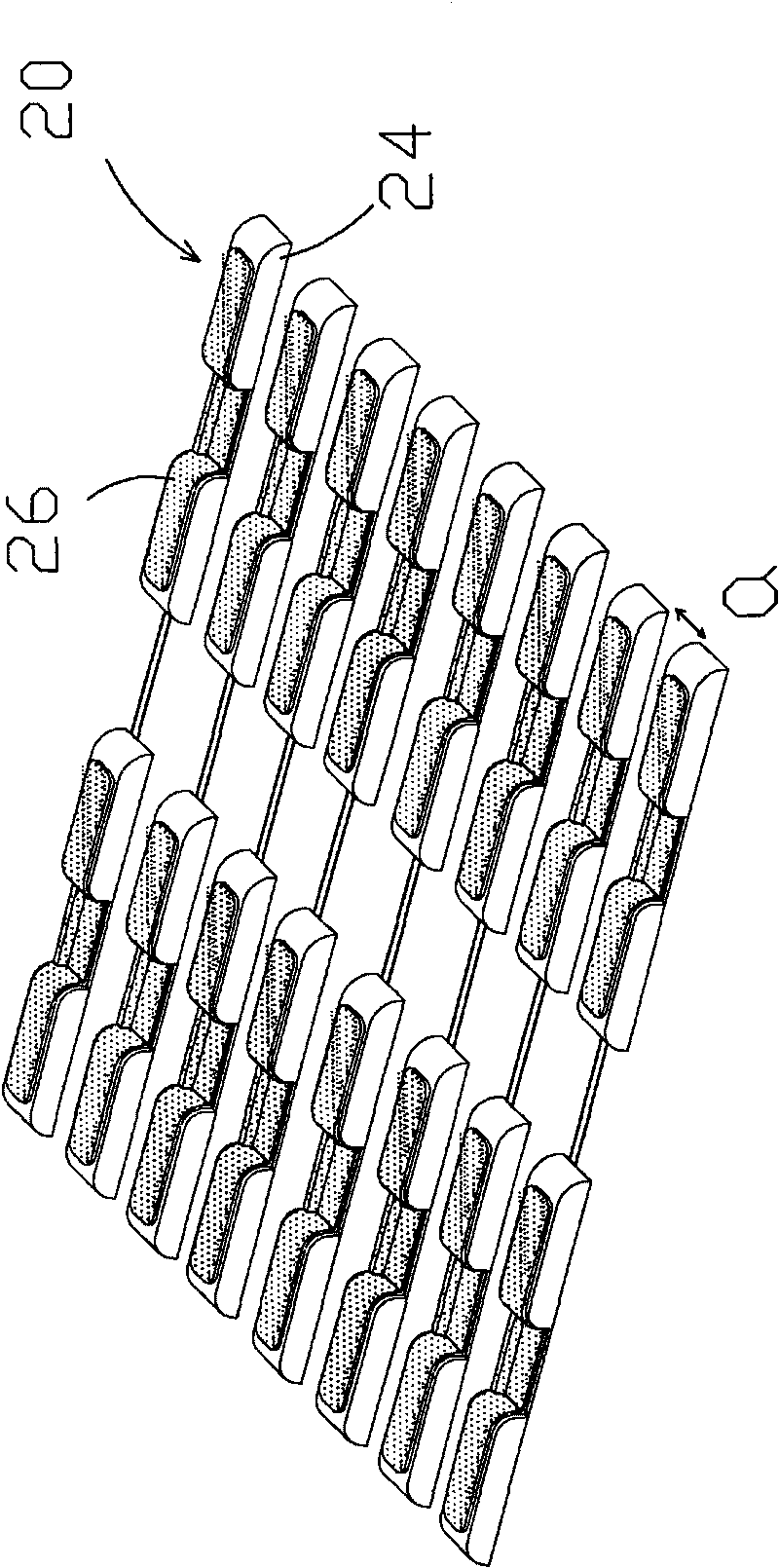

[0042] Please also refer to Figure 3(a) ~ Figure 3(c) , which is a schematic perspective view of the first embodiment of the present invention, a cross-sectional view of section line bb' and a schematic layout of the structure. The main technical difference between this embodiment and the existing smart bump is that a patterned elastic layer of the present invention bears at least two bump structures.

[0043]As shown in the figure, the structure of the smart bump 30 of the pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com