SOC (system on chip) chip and method for testing same

A system-on-chip, chip technology, applied in the field of communications, can solve the problem of inability to quickly test SOC chips effectively, and achieve the effect of improving accuracy and efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Functional Overview

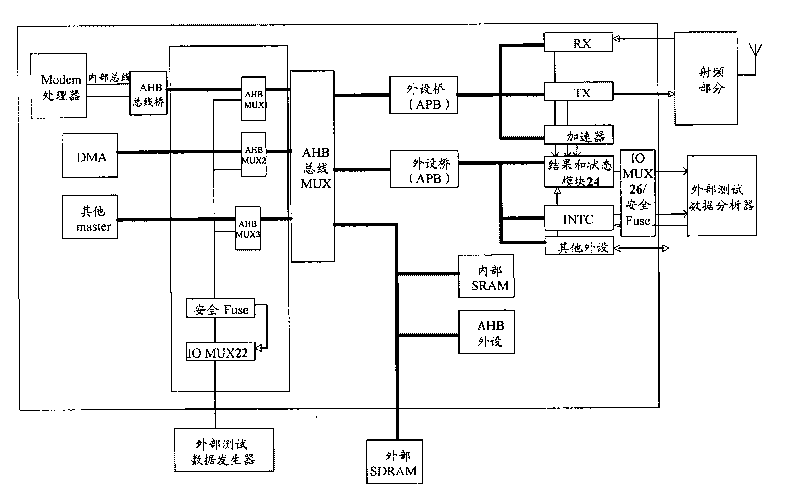

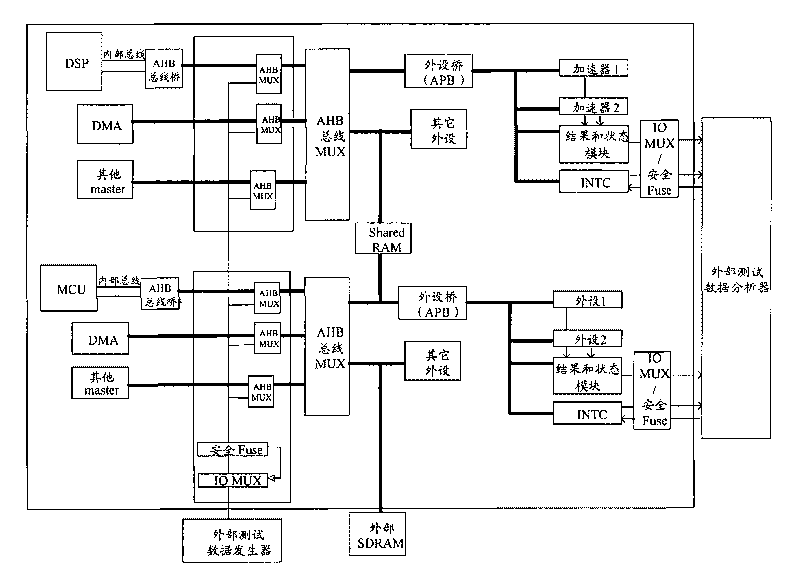

[0027] In the related art, since the system-on-chip cannot be tested quickly and effectively, the present invention improves the structure of the system-on-chip, and proposes a detection method based on the improved system-on-chip, and the specific processing is: external The test signal generator provides test vectors to the baseband chip; the first IO MUX and safety insurance wind the signal of the external test signal generator to the AHB bus MUX; the AHB bus MUX selects and drives different modules; The result of setting or accelerator is sent to the result and status module, and connected to the external test data analyzer by the second IOMUX; the external test data analyzer compares the received information with the known result obtained by simulation to judge whether the test is passed.

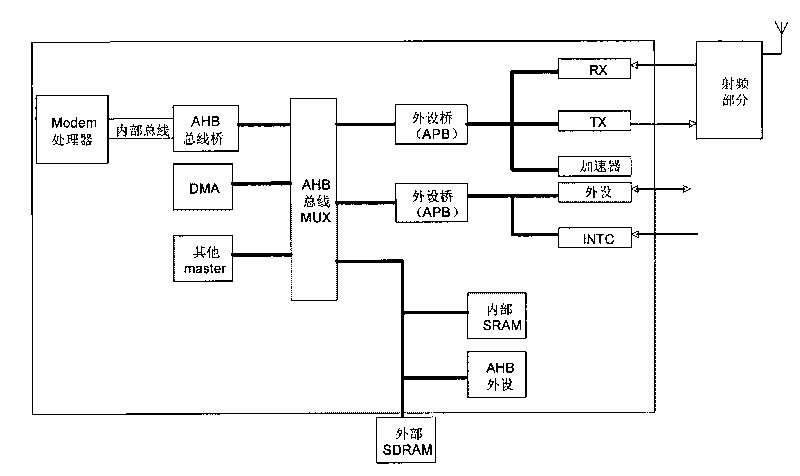

[0028] Before the above-mentioned processing procedure of the present invention is described in detail, the chip structure in the prior art is firstly desc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com