CMOS circuits with high-k gate dielectric

A dielectric and gate technology, applied in the field of CMOS structure, can solve problems such as structure and technology that have not yet been proposed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

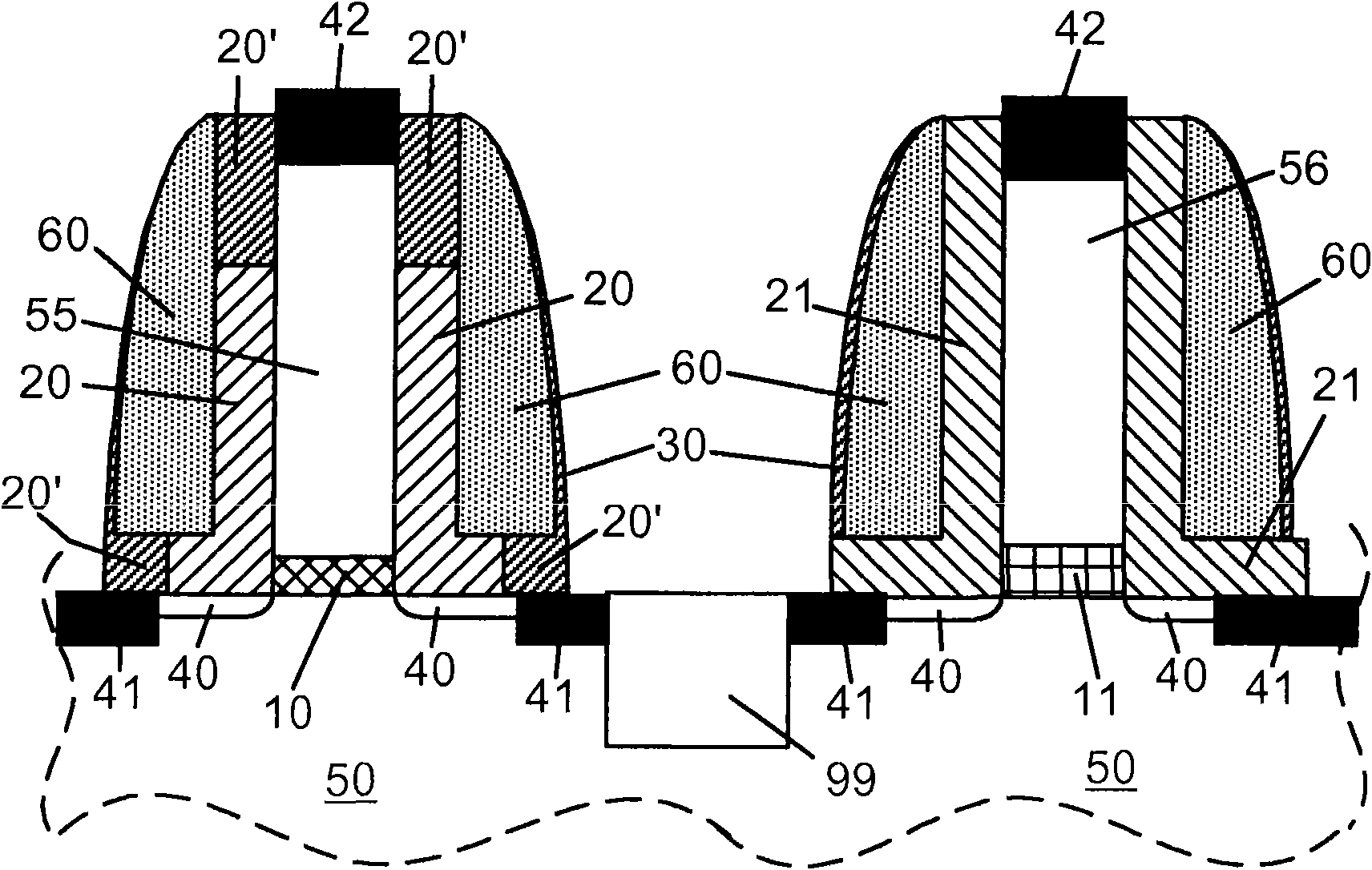

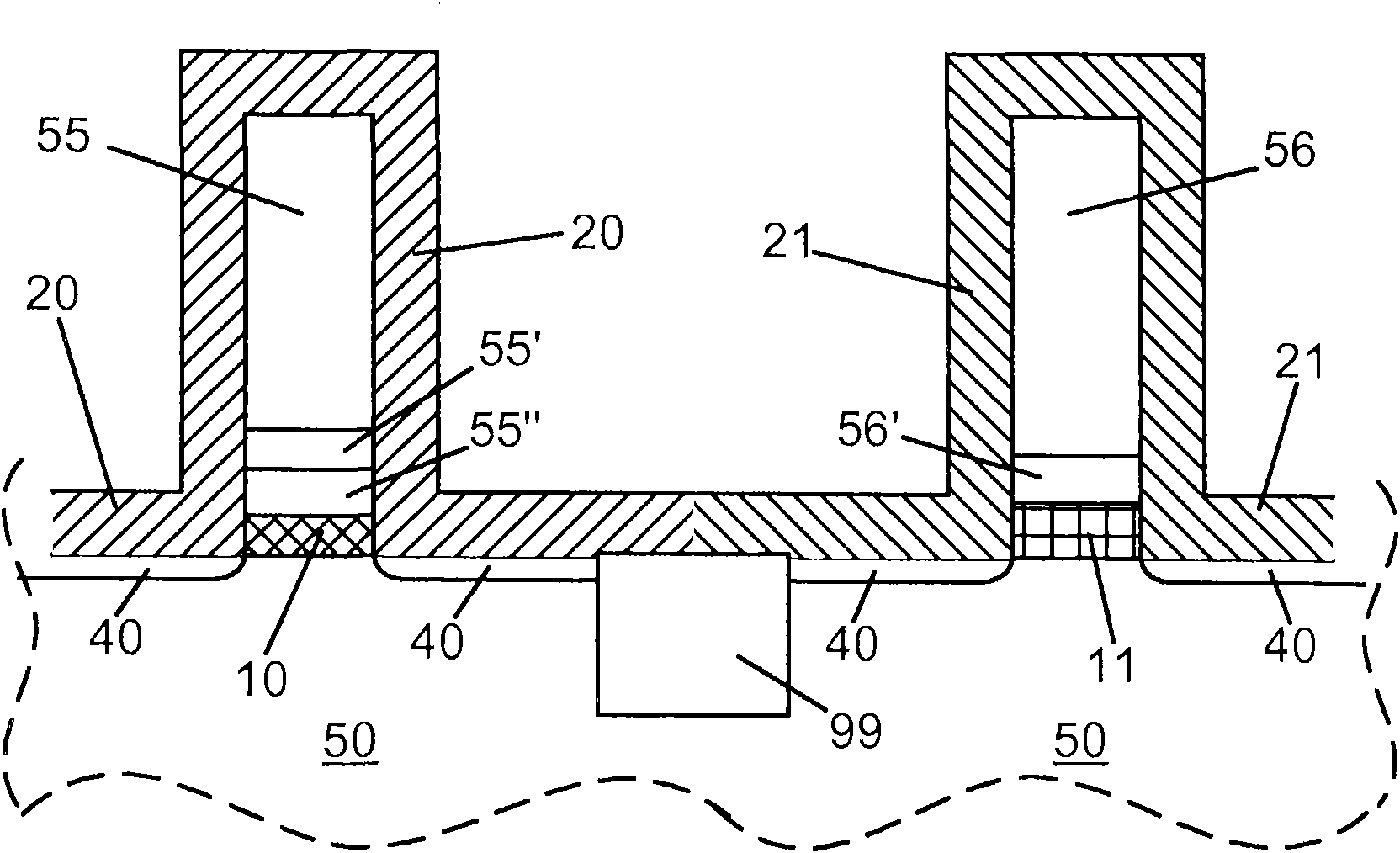

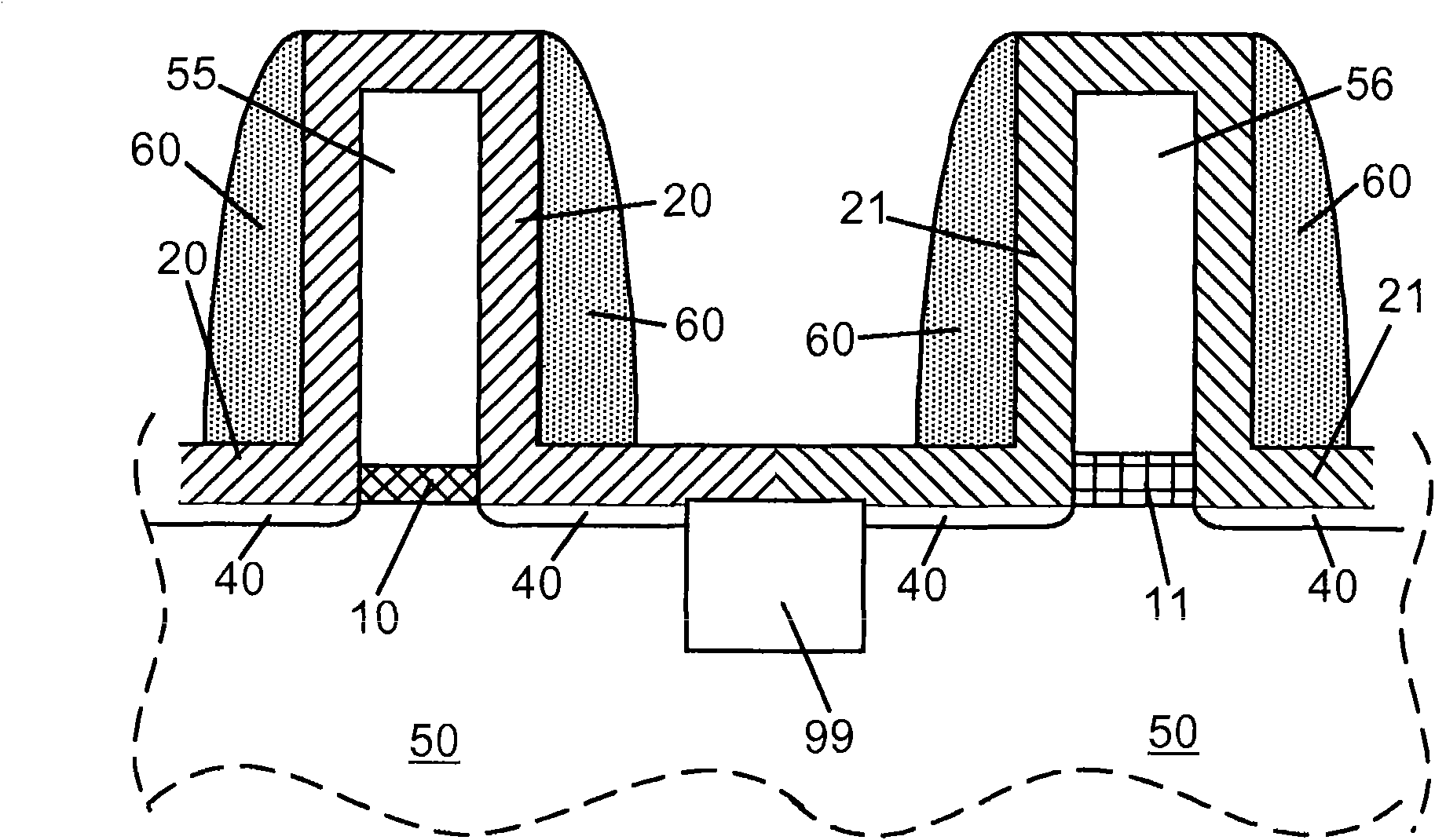

[0016] Field Effect Transistors (FETs) are considered well known in the field of electronics. The standard components of a FET are a source, a drain, a body between the source and drain, and a gate. The body is usually part of a substrate and is often referred to as the substrate. A gate covers the body and is capable of inducing a conduction channel in the body between the source and drain. In general nomenclature, channels are provided in the body. The gate is isolated from the body by a gate insulator. There are two types of FET devices: the hole-conducting type, known as a PFET; and the electron-conducting type, known as an NFET. Typically and exclusively, PFET and NFET devices on the same chip are wired as CMOS circuits. The CMOS circuit includes at least one PFET and at least one NFET device. When manufacturing or processing, when PFET and NFET devices are fabricated together on the same chip, you are actually dealing with CMOS processing and fabricating CMOS struct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com