Method for obtaining circuit performance after considering related stress of layout

A technology of layout and stress, applied in the field of obtaining the influence of stress introduced by STI process on circuit characteristics, to achieve the effects of accurate stress calculation, simplified grid update process, and simulation speed and scale.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

[0034] A method for obtaining circuit performance after consideration of layout-related stress proposed by the present invention comprises the following steps:

[0035] 1) Extract the region of each transistor in the published figure; the specific steps are:

[0036] 11) Layout division

[0037] In the entire layout range, detect the overlapping area of the layout layer corresponding to the polysilicon and the active area, and each obtained independent overlapping area corresponds to a transistor channel area (that is, the core area of the transistor); figure 1 It is a circuit (buffered SR flip-flop circuit) of an embodiment of the present invention, shown in the figure that the circuit includes 16 transistors M1-M16; figure 2 It is the layout corresponding to the circuit of this embodiment, and the figure shows that 16 independent overlapping regions correspond to 16 transistor channel regions M1-M16. figure 2 Only the active region layer (the dot matrix area in the f...

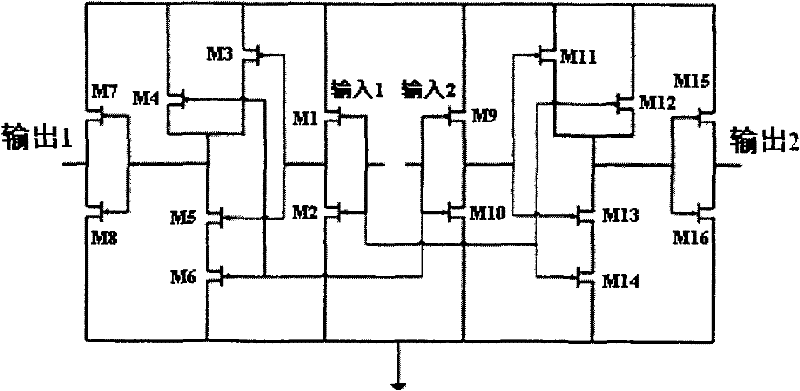

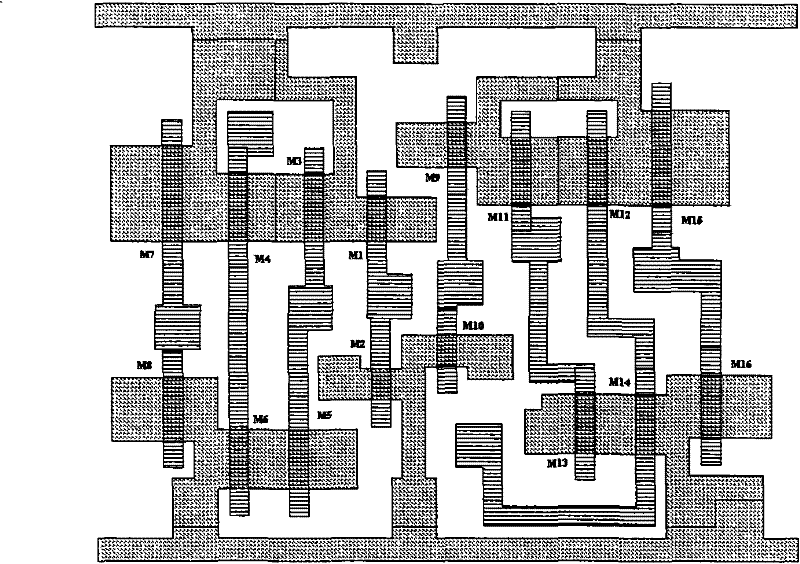

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com