A device for extending the capacity of access queue by distribution control

A memory access queue and distributed control technology, applied in machine execution devices, concurrent instruction execution, etc., can solve the problems of reducing the resource utilization rate of execution components, weakening the granularity of out-of-order transmission, and unable to fully utilize the resources of memory access components. capacity, performance improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

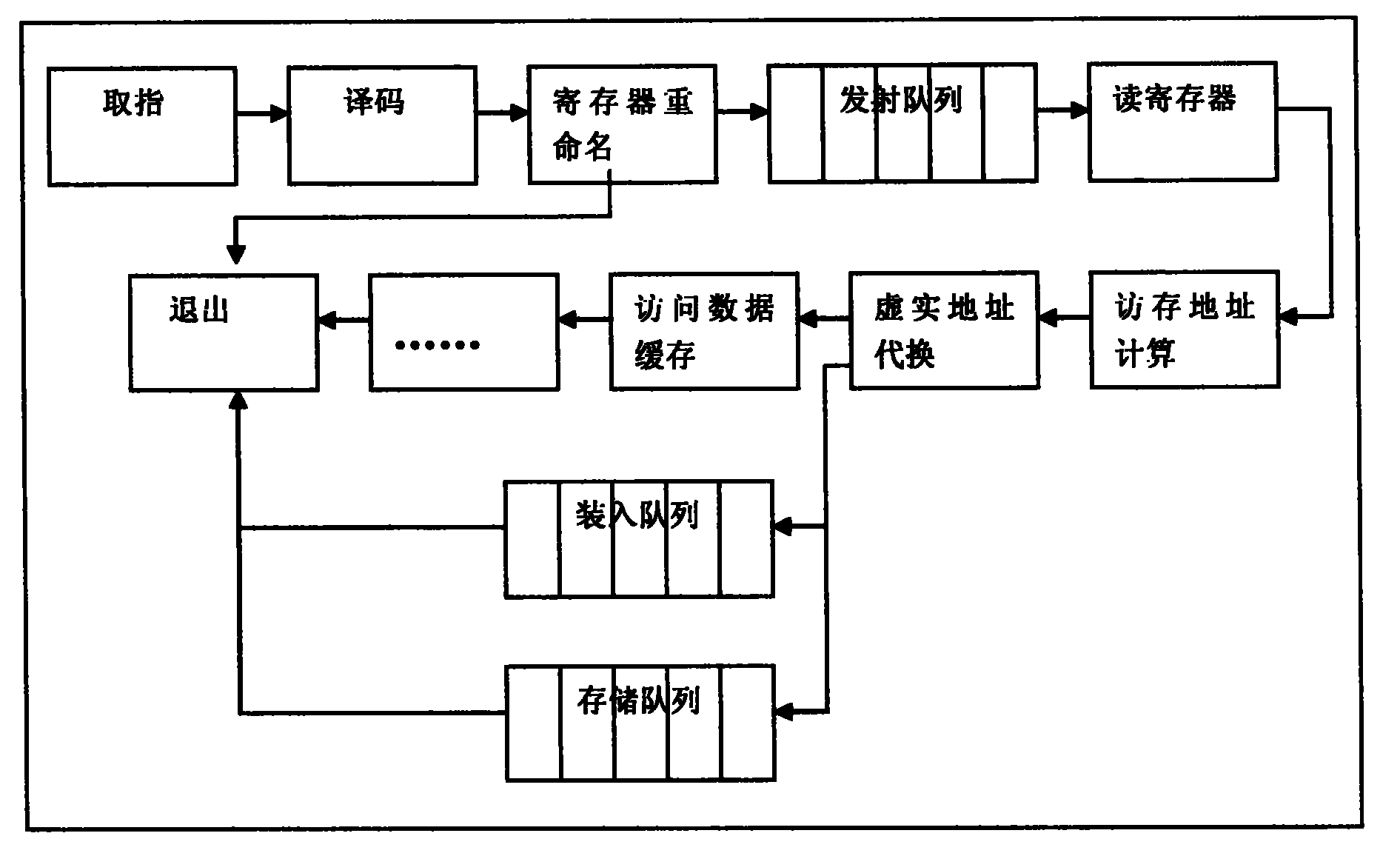

[0011] The device of the patent includes setting a memory access queue entry allocator on the register renaming platform of the microprocessor, and setting a memory access instruction transmitting controller on the transmitting platform. Wherein, the memory access queue entry allocator provided at the register renaming platform of the microprocessor includes: using the memory memory queue as a circular queue, setting a head pointer for the loading queue and the storage queue respectively, after resetting, the head pointers are all If it is "0", it means that the 0th entry will be assigned to the corresponding memory fetch instruction. When a load command is encountered in the register renaming platform, first check whether the load queue entry numbers carried by all load commands in the current emission queue are the same as the entry number pointed to by the load queue head pointer, if one of them is the same, then No new entry can be allocated for this load instruction and m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com