Multiprocessor system and Cache consistency message transmission method

A multi-processor system and message transmission technology, applied in memory systems, electrical digital data processing, instruments, etc., can solve the problems of lack of Cache consistency message transmission support, limit the application range of processors, etc., to reduce complexity and improve Compatibility, the effect of expanding the range of use

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

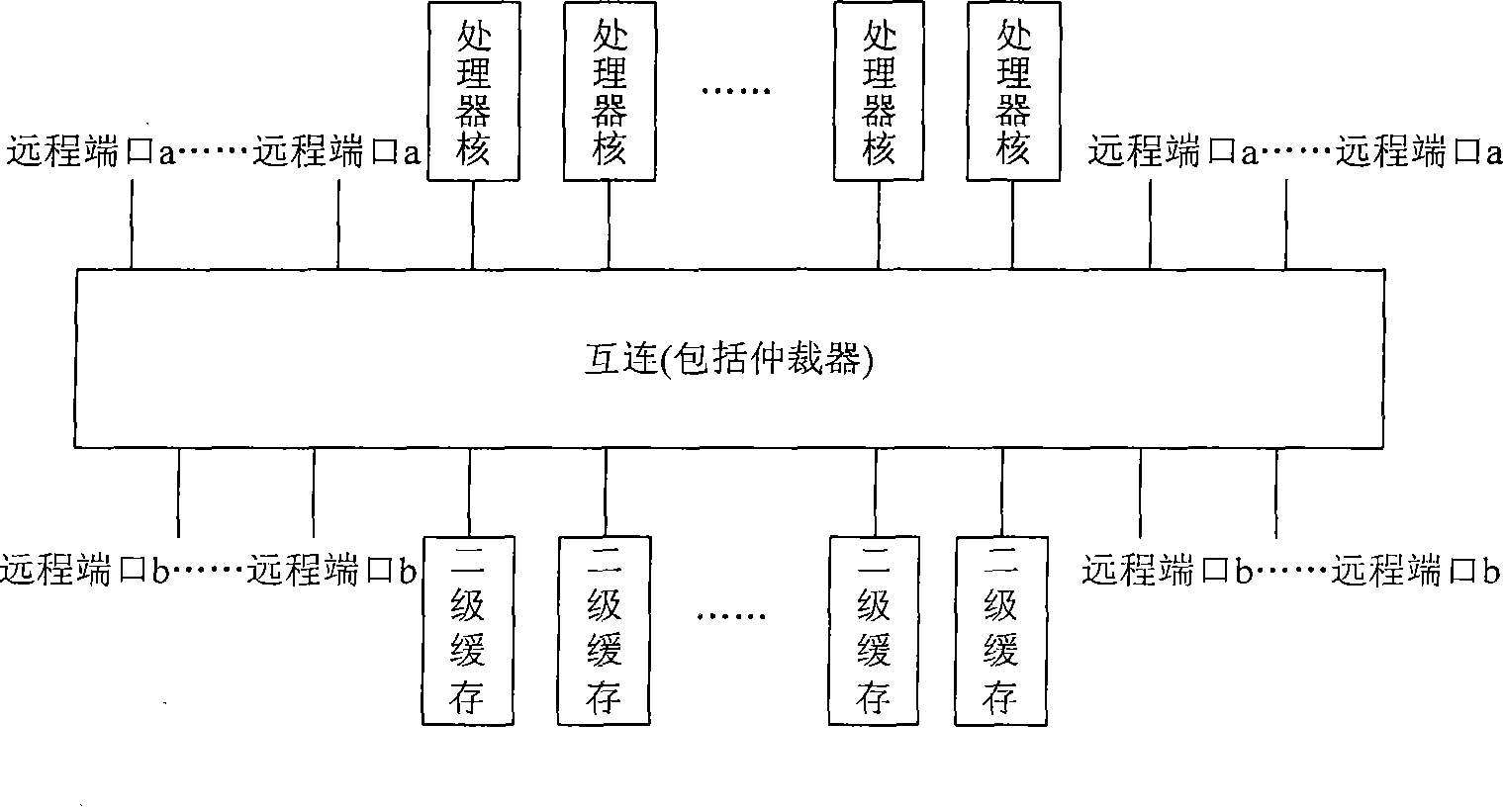

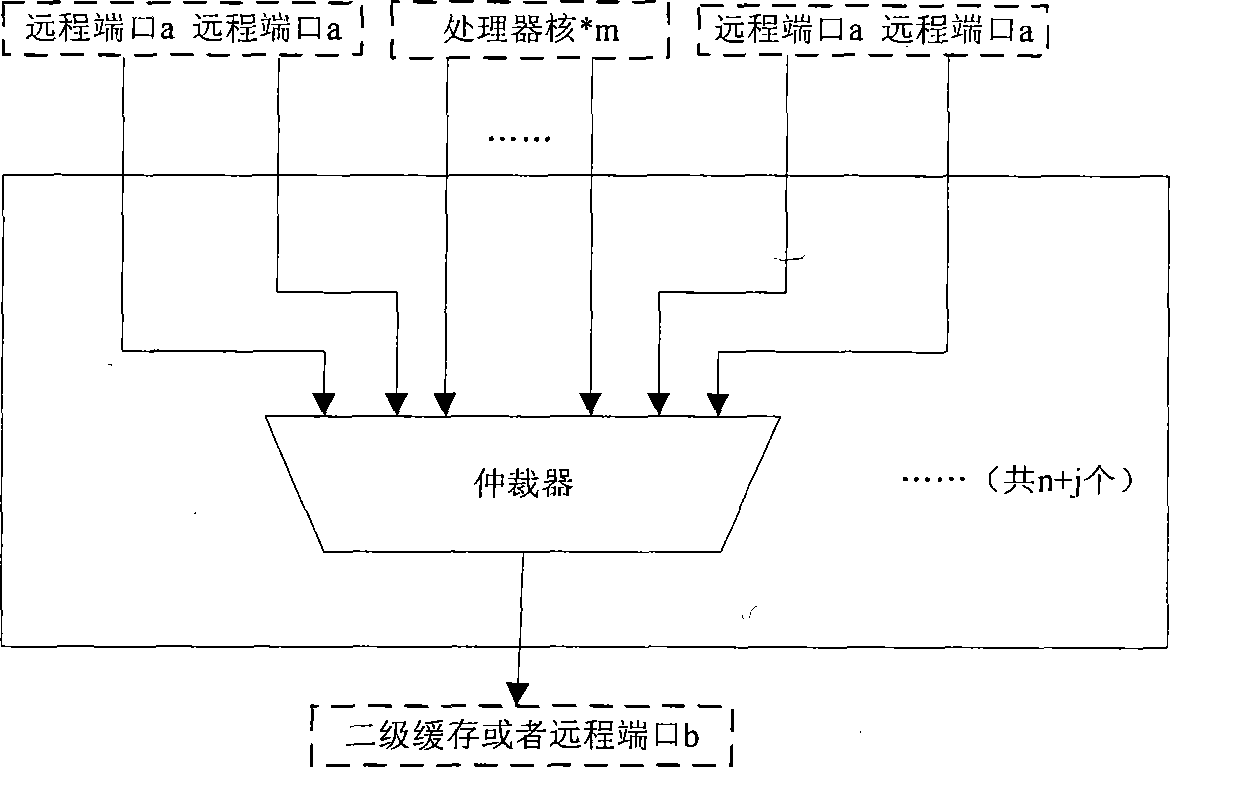

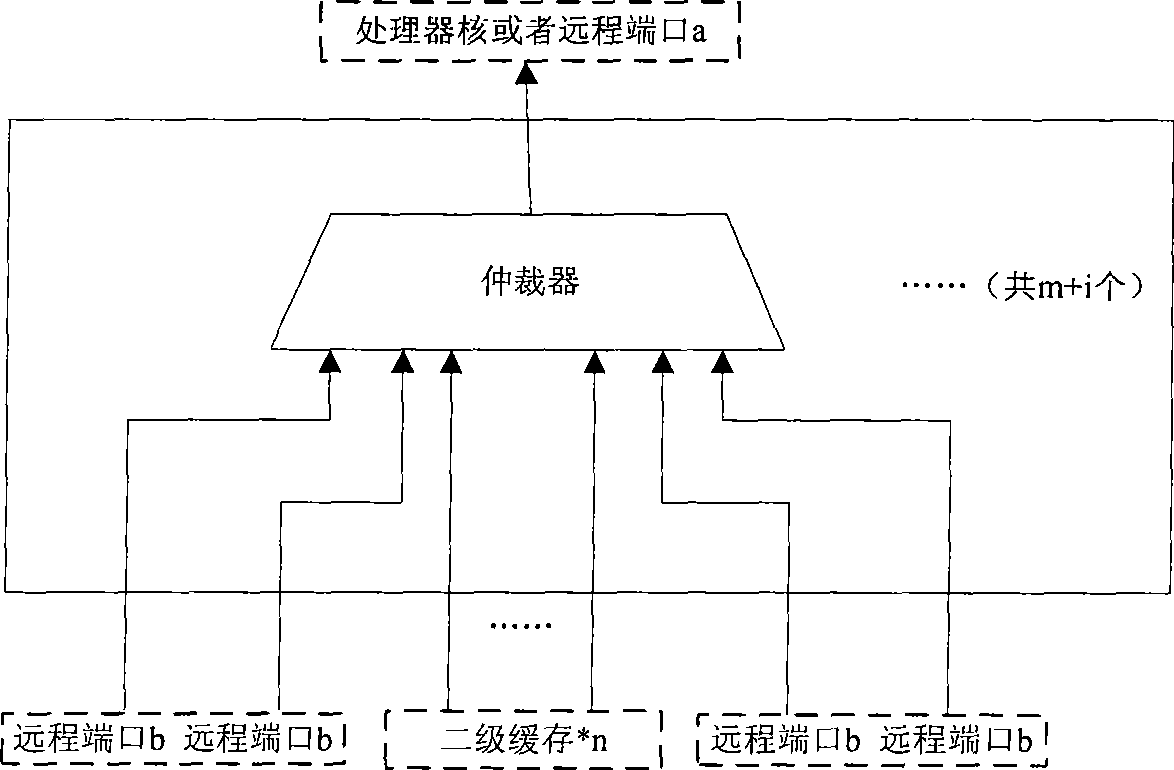

[0056] In order to better describe the present invention, in figure 1 A typical configuration scheme of an on-chip multiprocessor to which the method of the present invention can be applied is given in . In this figure, there are m processor cores with L1 caches and n L2 caches, where m and n are positive integers. The processor core and the second-level cache are connected through an interconnection network. The interconnection network described here can include direct connection, bus, crossbar, Mesh network, Torus network, star network, and tree network from the perspective of network topology. , a ring network and a hybrid network composed of one or more of the above-mentioned interconnection structures. The interconnection network is a connection line composed of address lines, data lines and other lines in terms of hardware structure. Thi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com