Loading plate structure for embedded burying semiconductor chip

A carrier board and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device parts, electric solid-state devices, etc., can solve problems such as damage to semiconductor chips, uneven filling of adhesive materials, excessive stress on the periphery of semiconductor chips and the periphery of openings, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The implementation of the present invention is described below through specific examples, and those skilled in the art can easily understand other advantages and effects of the present invention from the content disclosed in this specification.

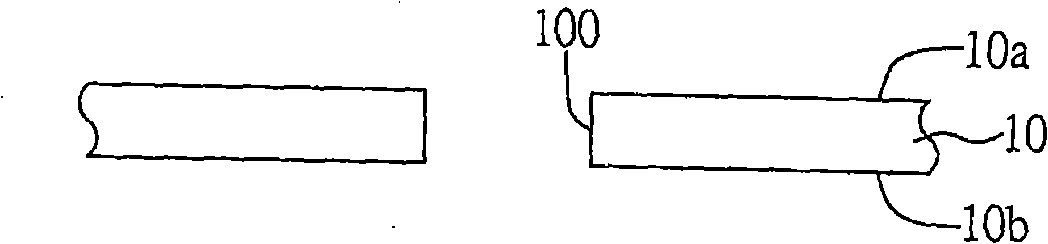

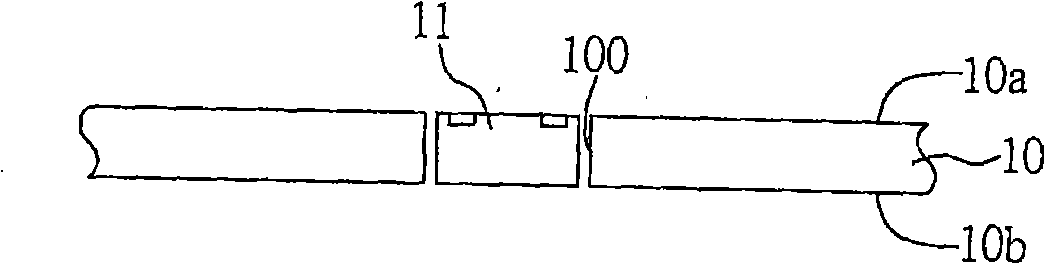

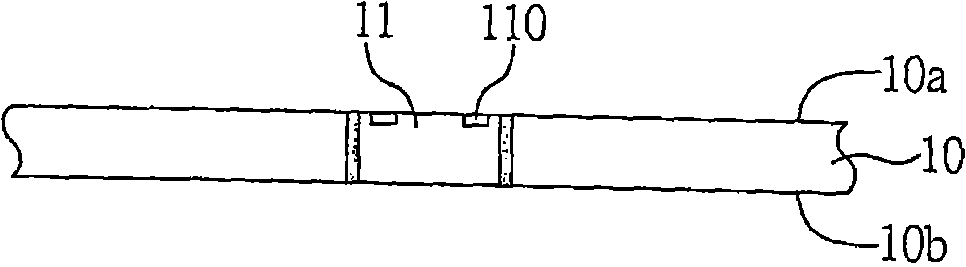

[0046] Figure 3A to Figure 3E Shown is the manufacturing process of the first embodiment of the carrier board structure for embedding semiconductor chips of the present invention.

[0047] As shown in FIG. 3A , first, a carrier plate 20 having a first surface 20 a and a second surface 20 b opposite to the first surface is provided, and at least one opening 21 with a chamfer 210 is formed in the carrier plate 20 , And the opening 21 is circular or rectangular, and the opening 21 runs through the first and second surfaces 20 a and 20 b of the carrier board 20 , and the chamfer 210 is a full chamfer. In this embodiment, the opening 21 is formed by one of cutting, stamping, laser and other forming methods.

[0048] In this embod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com