Device and method for in-system programming for programmable logic device

A programming logic and system programming technology, applied in memory systems, measuring devices, instruments, etc., can solve problems such as large storage units, poor fault tolerance, and inability to explicitly distinguish, and achieve the effect of solving large consumption of storage resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

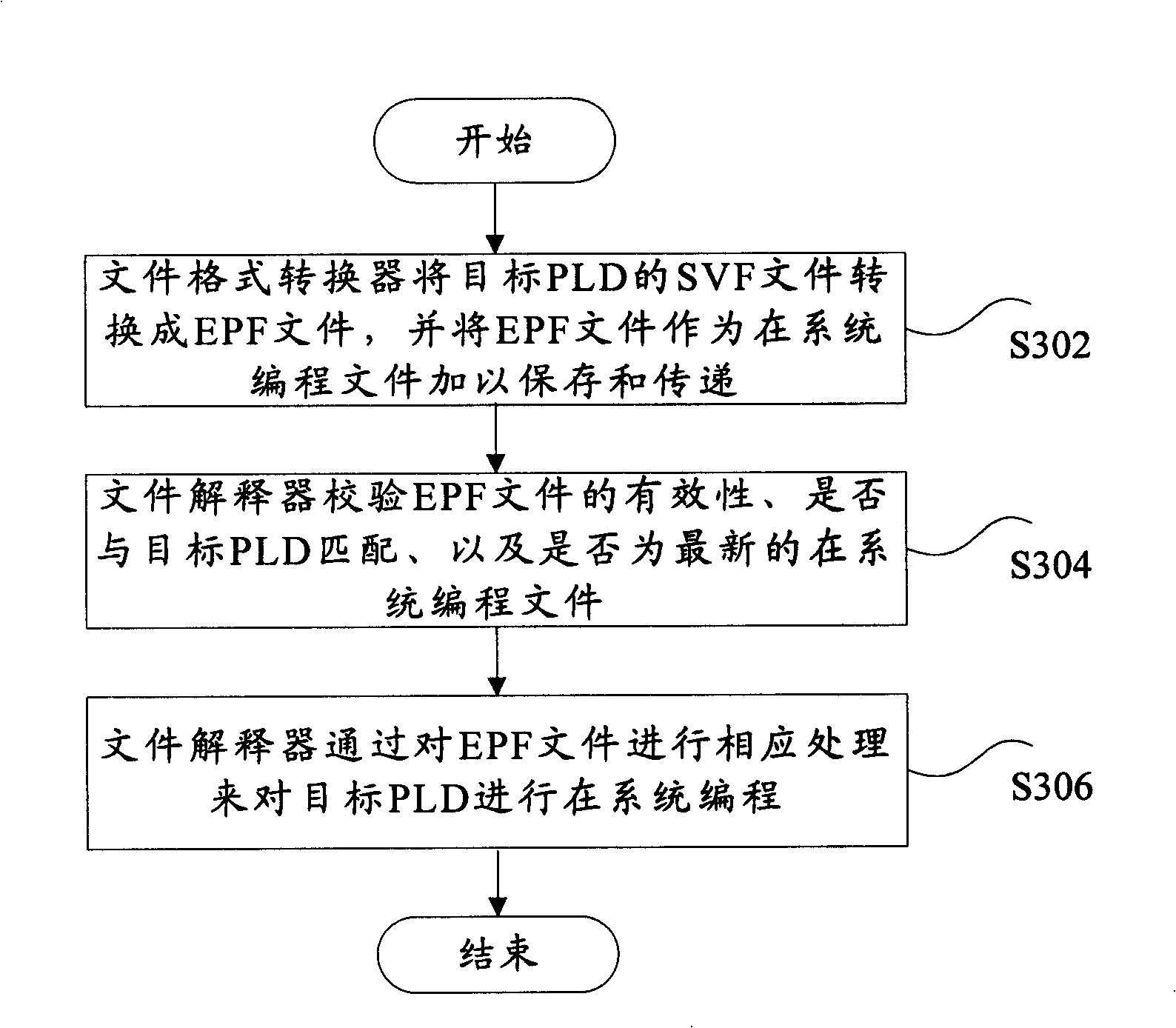

[0069] The following will combine Figure 5 The processing flow of the file format converter 102 will be described. Such as Figure 5 As shown, the processing of the file format converter 102 includes the following steps:

[0070] S1, open the SVF file of a target PLD, extract the instruction register length and various data register lengths of this PLD from SIR order, SDR order respectively;

[0071] S2, compare with the command register length and the data register length defined in their boundary scan description (BSD) files by all model PLDs, determine the model of the target PLD;

[0072] S3. If the SVF files of all target PLDs have been scanned, continue to S4, otherwise open the SVF file of the next target PLD in the daisy chain, and return to S1;

[0073] S4, process target PLD one by one, scan its SVF file;

[0074] S5. According to the instruction register length of all devices in the daisy chain and the position of the current target PLD in the daisy chain, calc...

example 2

[0099] The following will combine Figure 7 To describe the processing flow of the file interpreter 104. Such as Figure 7 As shown, the processing of file interpreter 104 includes the following steps:

[0100] S1. Perform CRC-16 calculation on the part of the EPF file other than the CRC-16 check information. If the calculation result is consistent with the CRC-16 check information in the EPF file, continue to execute S2, otherwise a CRC-16 check error will be prompted. , end the programming process;

[0101] S2, check the version information of the EPF file, if it matches the target PLD, continue to execute S3, otherwise it will prompt the file version verification error, and end the programming process;

[0102] S3, decompress the compressed data in the EPF file according to the Deflate algorithm, and restore the EPF programming data;

[0103] S4, in the EPF programming data, identify the command words represented by various symbol codes, according to

[0104] The "bit ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com