Integrated navigation computer based on DSP and FPGA

A combined navigation and computer technology, applied in the field of combined navigation, can solve the problems of unsatisfactory high real-time applications, interruption of time navigation calculation process, low integration level, etc., achieve good scalability, convenient transplantation and upgrading, and improve integration level Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

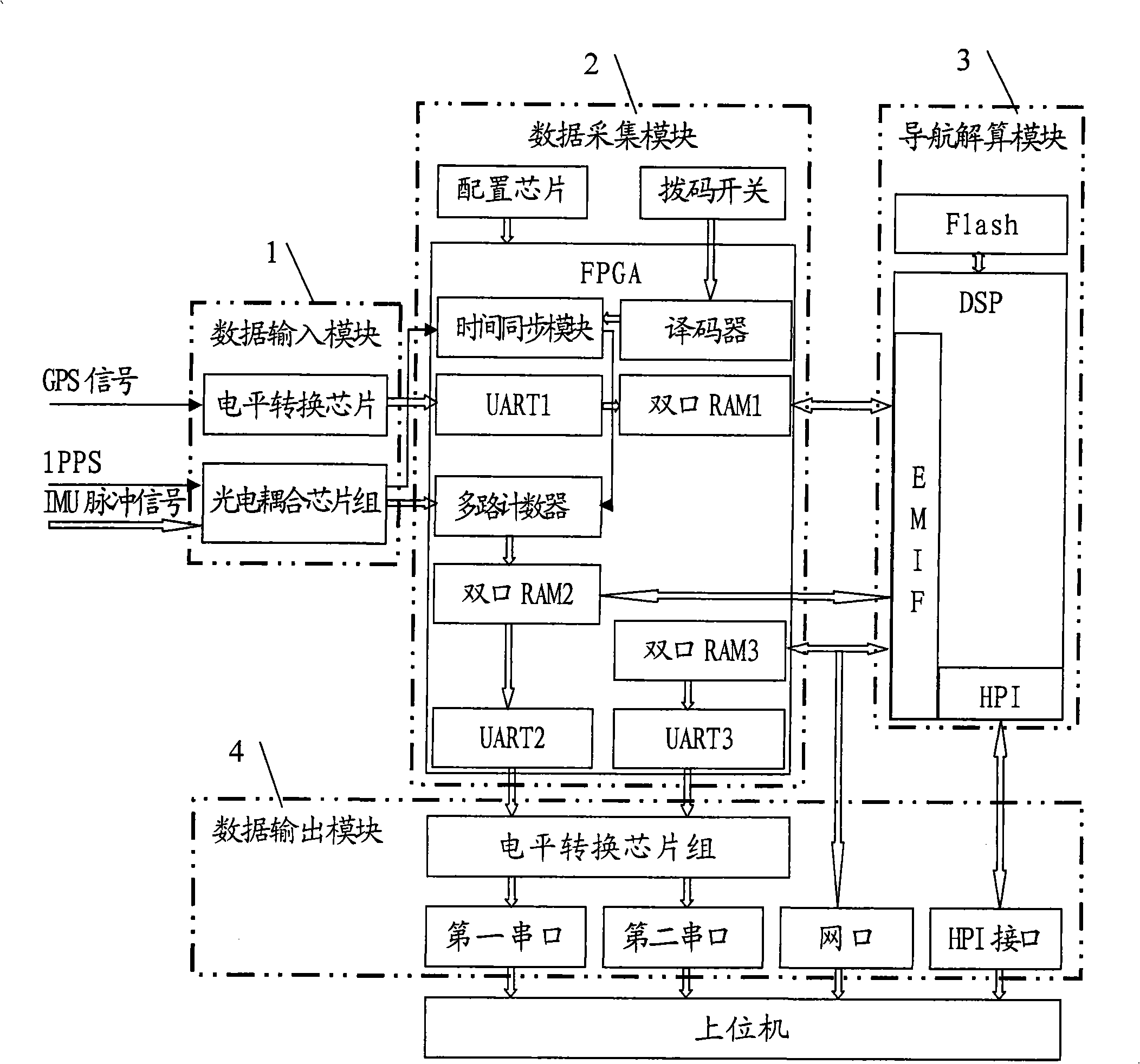

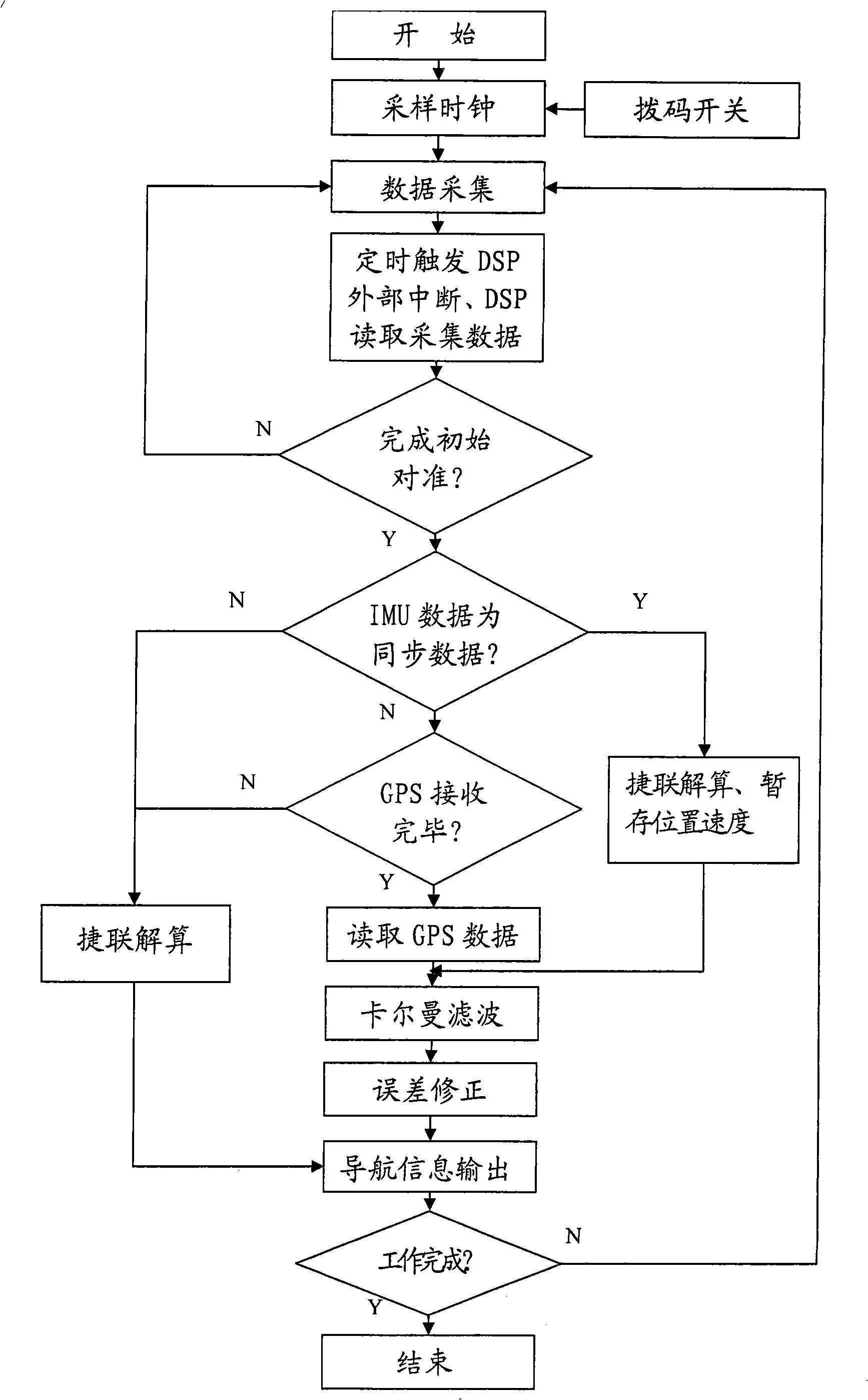

[0026] Such as figure 1 As shown, the present invention is composed of a data input module 1 , a data acquisition module 2 , a navigation calculation module 3 and a data output module 4 .

[0027] Described data input module 1 comprises level conversion chip and photoelectric coupling chipset, and level conversion chip adopts a MAX3232, and GPS signal outputs the GPS signal of CMOS level form after level conversion chip conversion; Photoelectric coupling chipset adopts 7 One piece of HCPL063L, one of which removes the noise of the 1PPS second pulse signal and outputs the 1PPS signal in the form of CMOS level, and the other 6 pieces remove the noise of the IMU pulse signal (including 6 pulse signals output by three accelerometers and three gyroscopes) Then output the IMU pulse signal in the form of CMOS level.

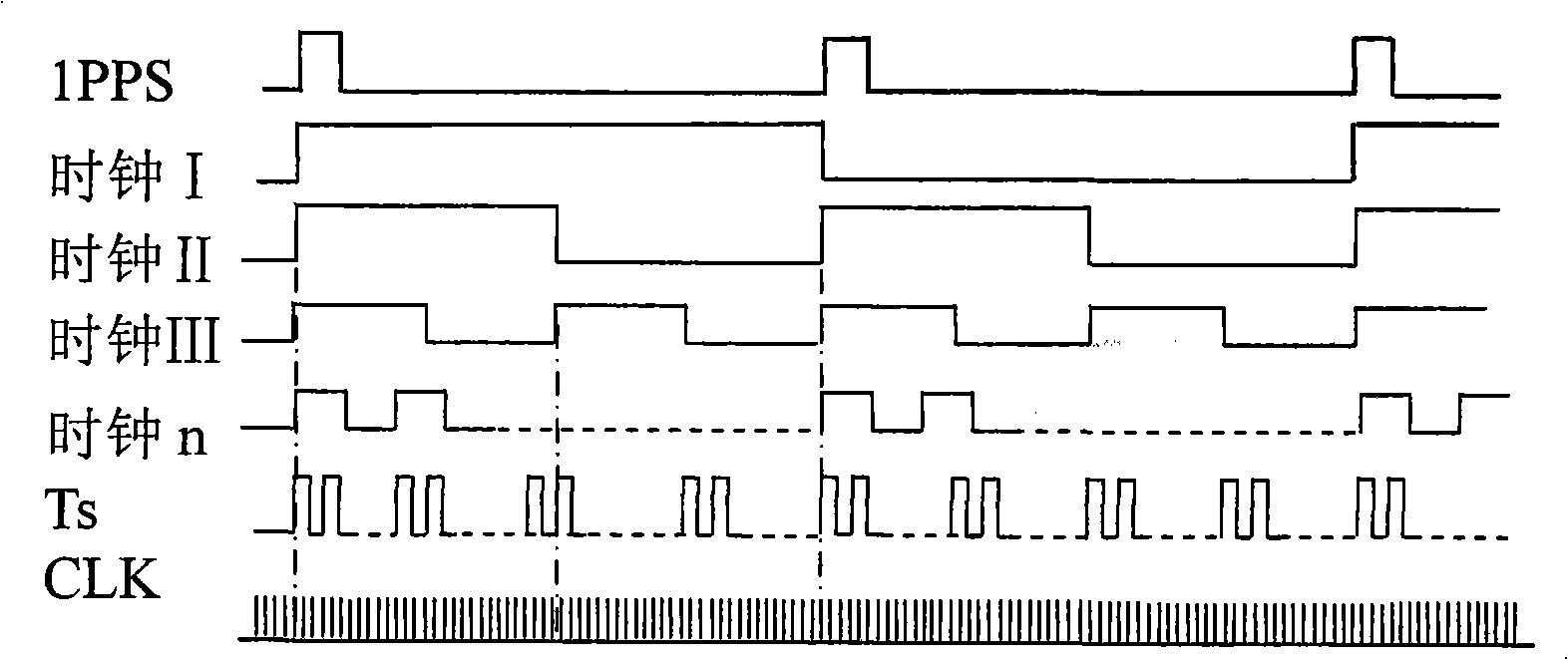

[0028] Described data collection module 2 comprises FPGA, configuration chip and dial switch, and wherein, FPGA comprises time synchronization module, decoder, multi-c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com