Image recognition accelerator and MPU chip possessing image recognition accelerator

A technology of image recognition and acceleration devices, which is applied in the direction of processor architecture/configuration, machine execution devices, character and pattern recognition, etc. It can solve the problems of narrow effective field of acceleration circuits, large differences in parameters and steps, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The various embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings:

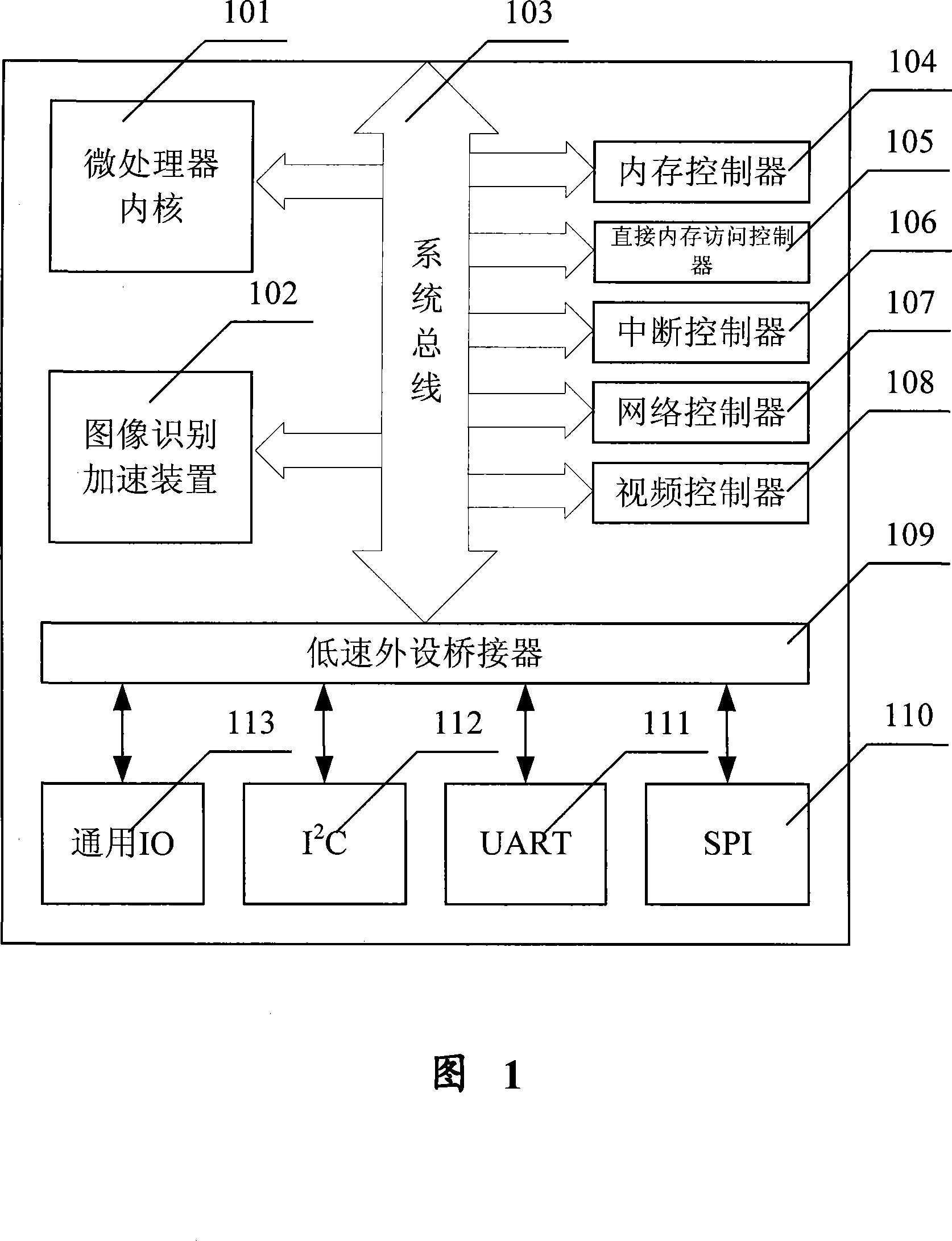

[0015] Fig. 1 is a block diagram of a microprocessor system according to an embodiment of the present invention. The figure describes in detail the internal system block diagram of an embedded processor chip adopting the present invention. The processor consists of a microprocessor core (101), an image recognition acceleration device (102), a system bus (103), a memory controller (104), a direct memory access controller (105), an interrupt controller (106), and a network Controller (107), video controller (108), low-speed peripheral bridge (109) for connecting low-speed peripherals, and general-purpose IO (113), I 2 C bus controller (112), UART controller (111) and SPI controller (110) are formed. The microprocessor core may be a commercial IP core such as ARM9 or ARM11. In order to meet performance requirements, the microprocessor core general...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com