Polymetal interconnecting layer combined aerial on chip

A technology of combining antenna and interconnect layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The embodiments of the present invention are described in detail below in conjunction with the accompanying drawings: this embodiment is implemented on the premise of the technical solution of the present invention, and detailed implementation methods and specific operating procedures are provided, but the protection scope of the present invention is not limited to the following the described embodiment.

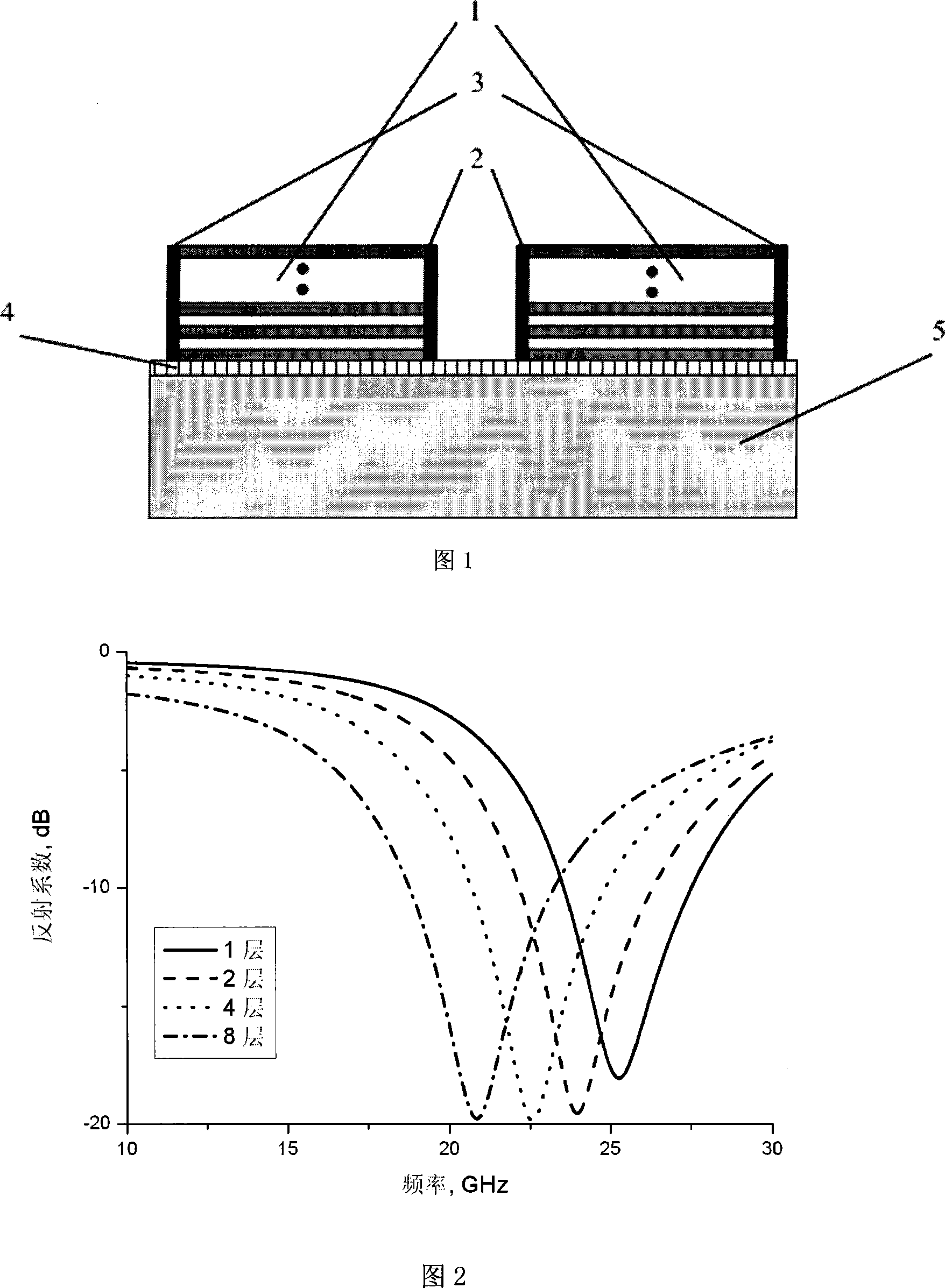

[0017] As shown in FIG. 1 , this embodiment includes: a multi-metal interconnection layer radiating element 1 , a feed through hole 2 , a short circuit through hole 3 , a silicon dioxide layer 4 and a silicon substrate 5 . The silicon substrate 5 is located at the bottom, the silicon dioxide layer 4 is above it, and the multi-metal interconnection layer radiation element 1 , feed through hole 2 and short circuit through hole 3 are above it. The center of the multi-metal interconnection layer radiating element 1 is connected to the feed through hole 2 , and both ends a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com