Semiconductor package structure

A packaging structure, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device parts, electric solid-state devices, etc., can solve the problems of increasing the probability of chip damage, increasing the size of the packaging structure, inconvenience, etc., to reduce chip damage The probability of electromagnetic interference shielding and the effect of overcoming electromagnetic interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

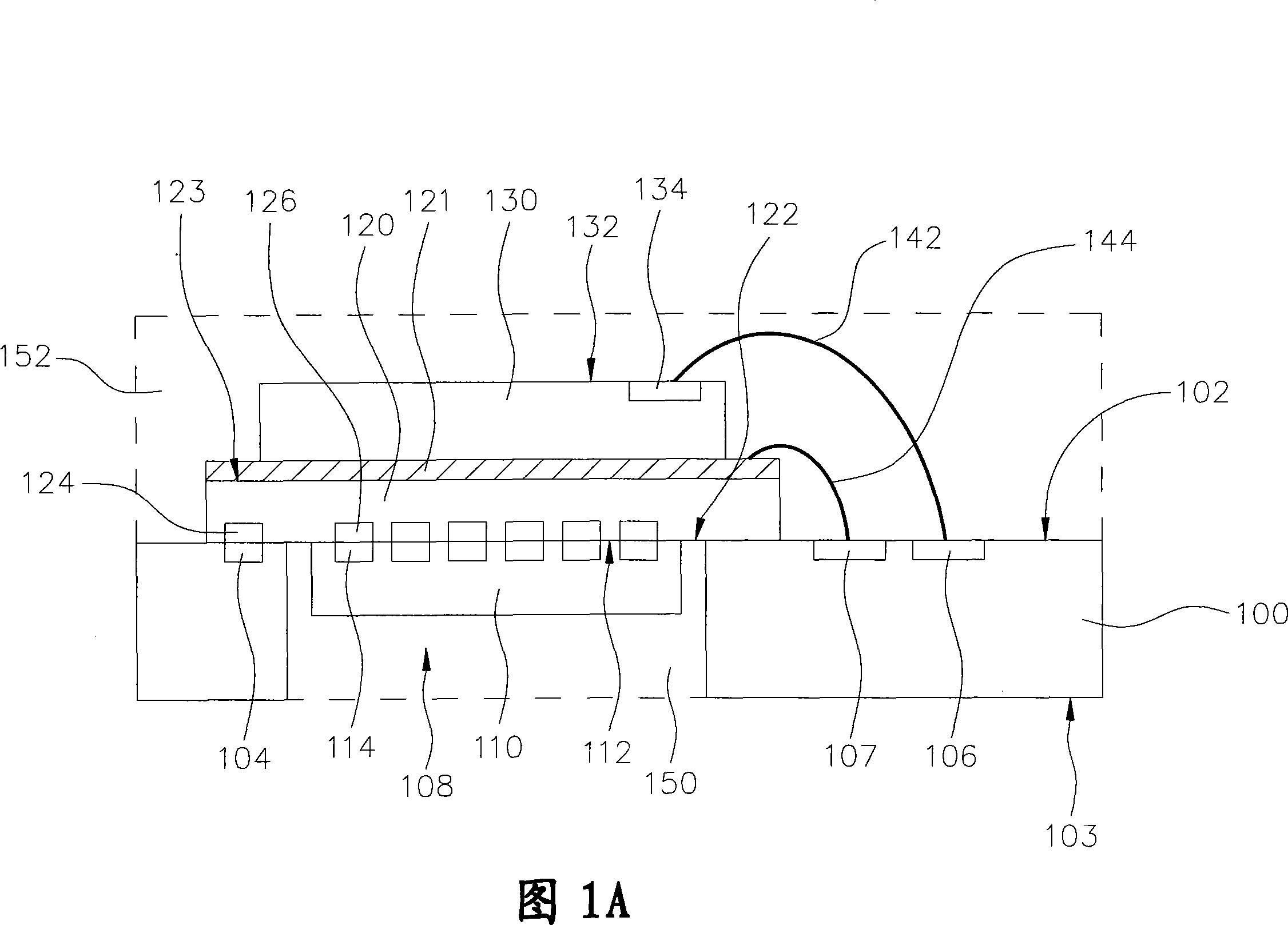

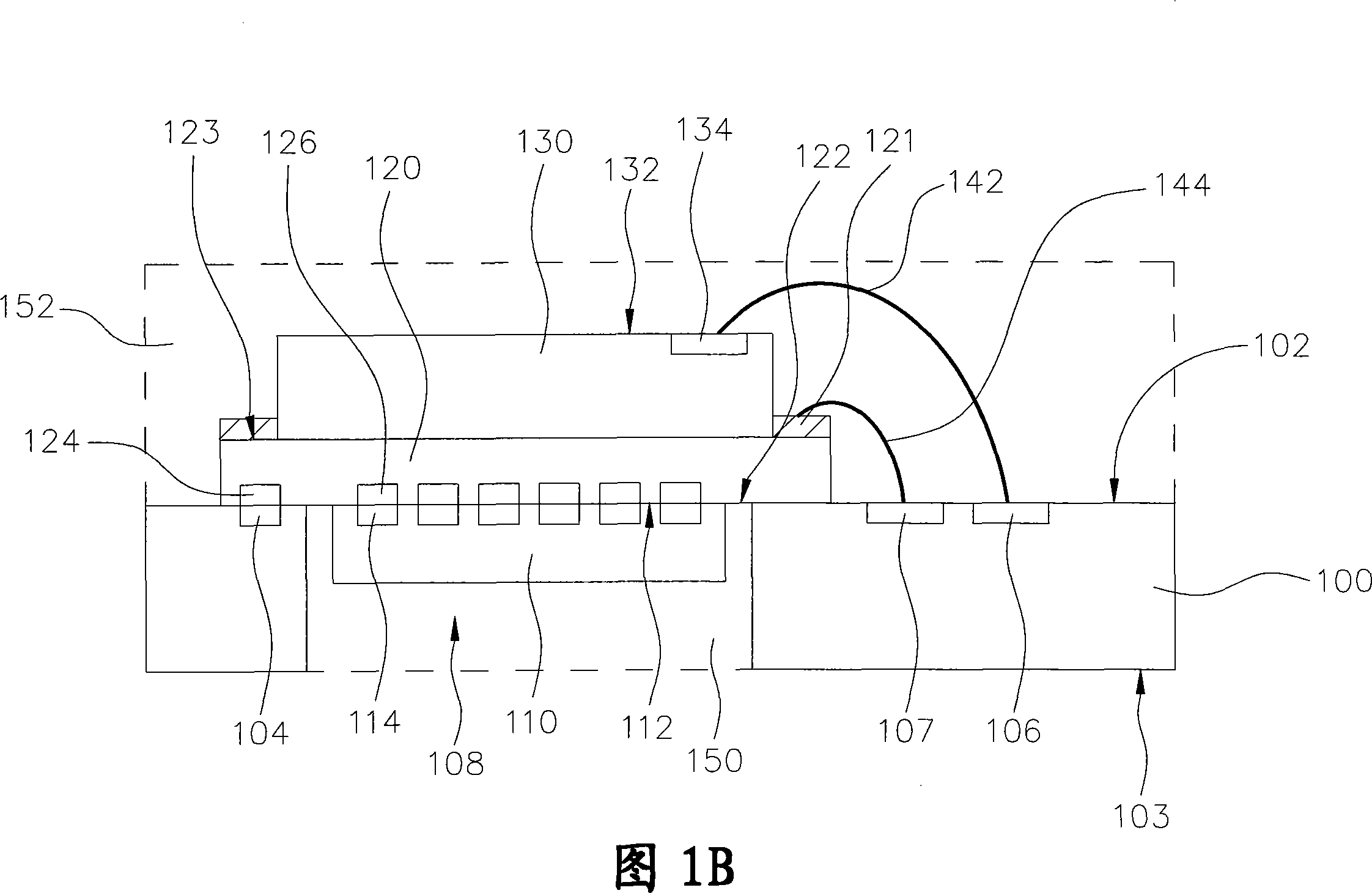

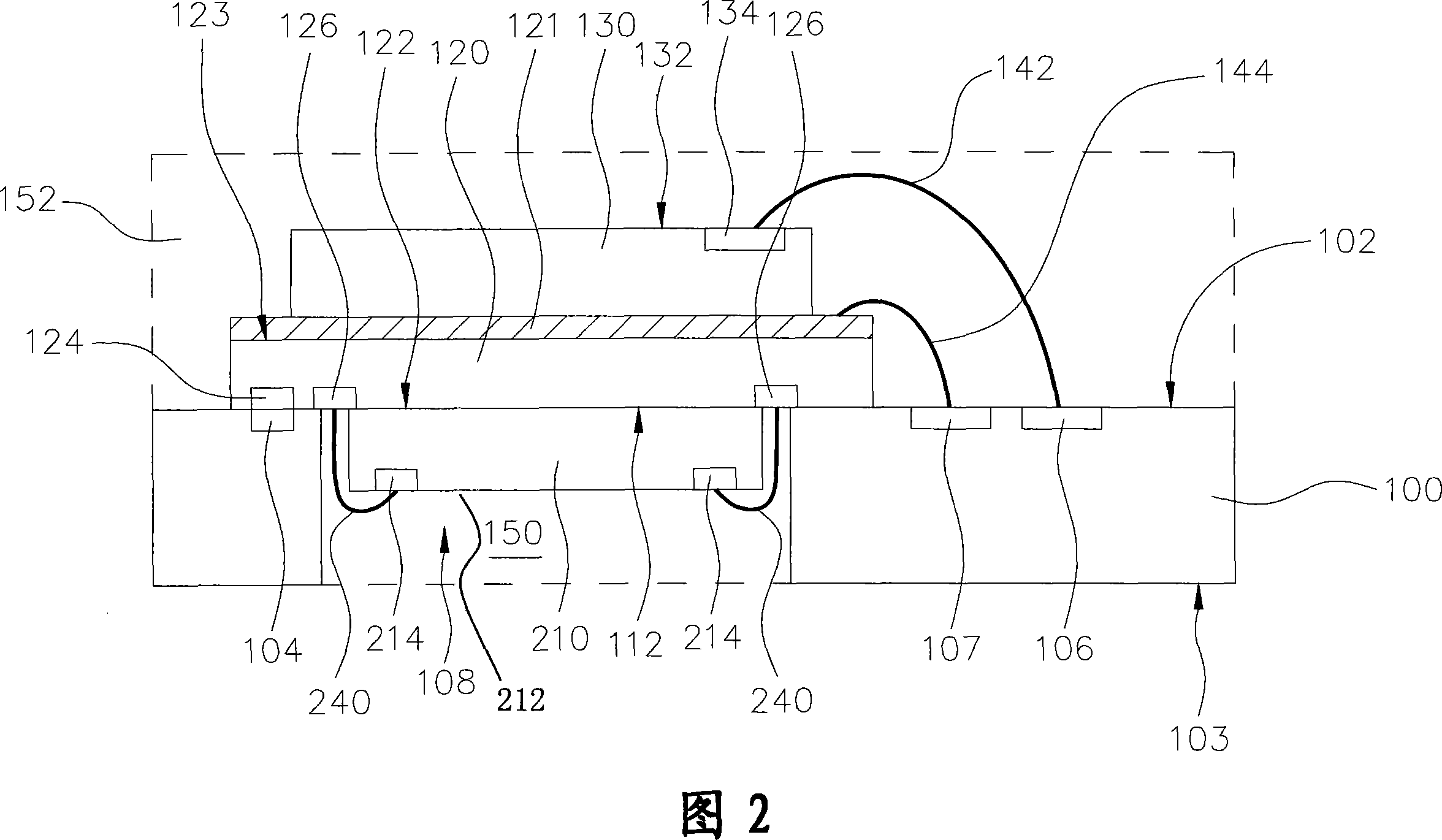

[0032] In order to further explain the technical means and effects of the present invention to achieve the intended purpose of the invention, the following describes the specific implementation, structure, steps, features and the semiconductor package structure of the present invention with reference to the drawings and preferred embodiments. Efficacy, as detailed below.

[0033] The foregoing and other technical content, features, and effects of the present invention will be clearly presented in the following detailed description of the preferred embodiment with reference to the drawings. Through the description of the specific embodiments, it is possible to gain a more in-depth and specific understanding of the technical means and effects adopted by the present invention to achieve the predetermined purpose. However, the accompanying drawings are only for reference and explanation purposes, and are not used for the present invention. Be restricted.

[0034] Although the present ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com