Printed wiring board and manufacturing method thereof

A technology for printed circuit boards and wiring layers, which is applied in the fields of printed circuit manufacturing, printed circuits, printed circuits, etc. It can solve the problems of insulation resistance degradation, easy accumulation of moisture, and increased connection resistance of the insulating layer, so as to prevent solder bumps from interacting with each other. Inter-short circuit, insulation and connection reliability are excellent, and the effect of suppressing the deterioration of insulation resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0106] Hereinafter, an example of the printed wiring board and its manufacturing method of the present invention will be described with reference to the drawings. First, refer to Figure 7 and Figure 8 The first embodiment of the printed wiring board of the present invention will be described.

[0107] Figure 7 Shows the cross section of the printed wiring board 10 (package substrate) before mounting the IC chip 90 as an electronic component, Figure 8 It shows the cross section of the printed wiring board 10 in the state which mounted the IC chip 90. Such as Figure 8 As shown, an IC chip 90 is mounted on the upper surface of the printed wiring board 10, and the lower surface is connected to the daughter board 94.

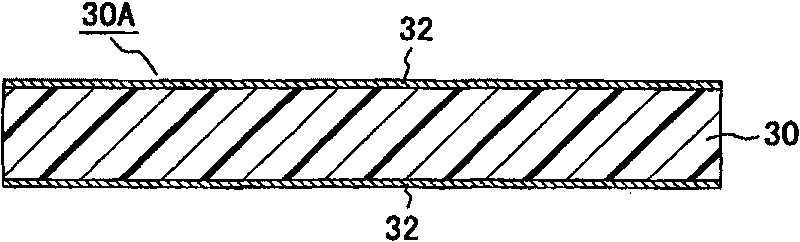

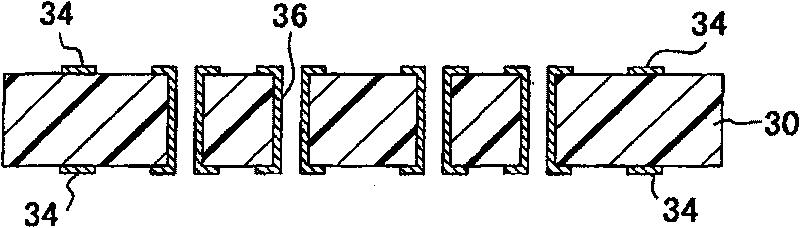

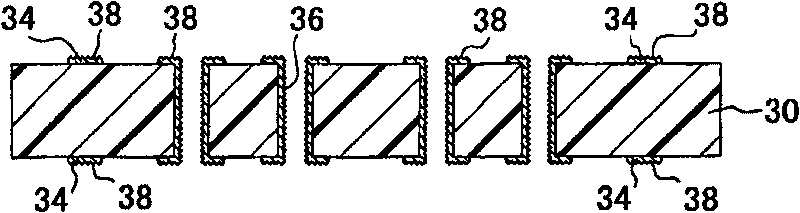

[0108] The printed wiring board 10 of this embodiment has a form in which build-up wiring layers 80A and 80B are formed on the front and back surfaces of the core substrate 30, respectively. The build-up wiring layer 80A is composed of an interlayer resin insulating...

Embodiment 2

[0177] The area of the solder resist layer (electronic component mounting area) corresponding to the area (C4 area) where the conductor pads for IC chip mounting are provided is 70 mm 2 , And the number of conductor pads provided in the mounting area was 2000 (the same as the number of electrodes of the IC chip), except that the printed wiring board was manufactured in the same manner as in Example 1.

[0178] In addition, the surface in the electronic component mounting area in this embodiment is formed as an uneven surface with a maximum roughness of 0.5 μm.

Embodiment 3

[0180] The area of the solder resist layer (electronic component mounting area) corresponding to the area (C4 area) where the conductor pad for IC chip mounting is provided is 130 mm 2 , And the number of conductor pads provided in the mounting area was 4000, except that the printed wiring board was manufactured in the same manner as in Example 1.

[0181] In addition, the surface in the electronic component mounting area in this embodiment is formed as an uneven surface with a maximum roughness of 0.4 μm.

PUM

| Property | Measurement | Unit |

|---|---|---|

| surface roughness | aaaaa | aaaaa |

| surface roughness | aaaaa | aaaaa |

| surface roughness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com