Method for flash technology high-voltage bar oxygen and tunnel-penetration oxidation layer

A technology of tunneling oxide layer and gate oxide layer, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of reduced erasability, failure, and inability to erase, and achieve the goal of increasing the erasable number of times Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

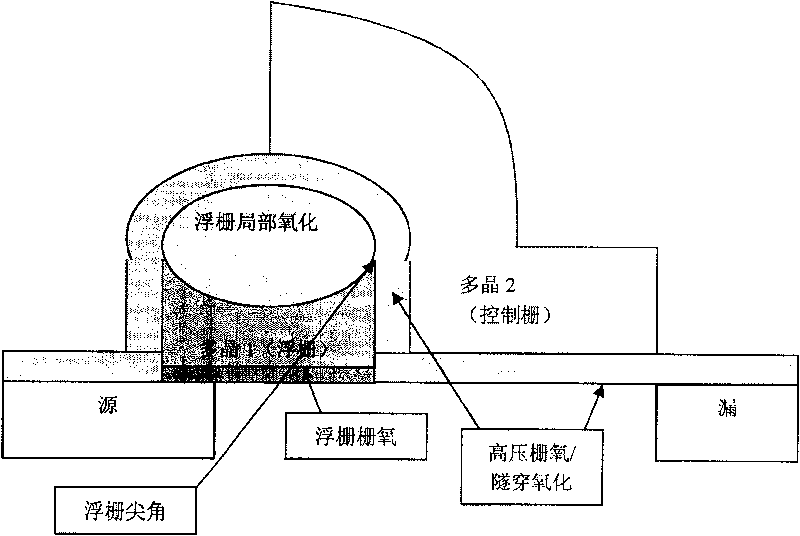

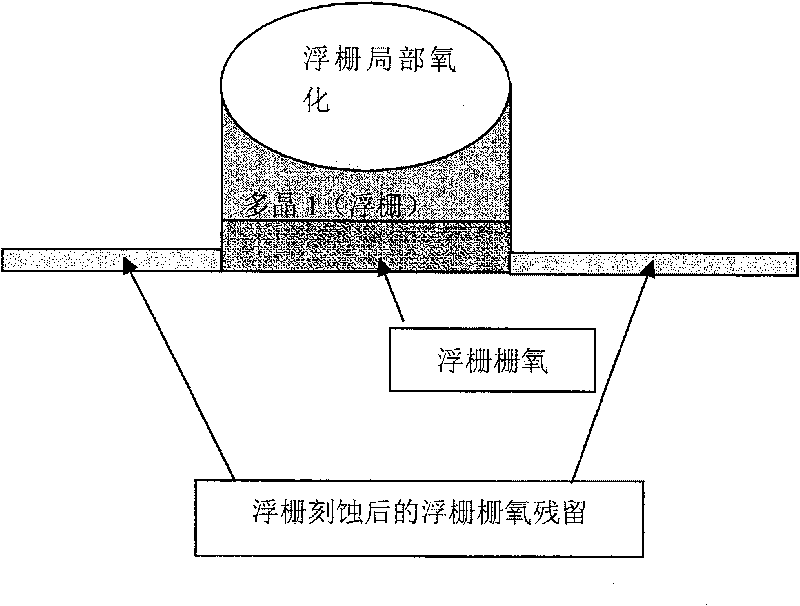

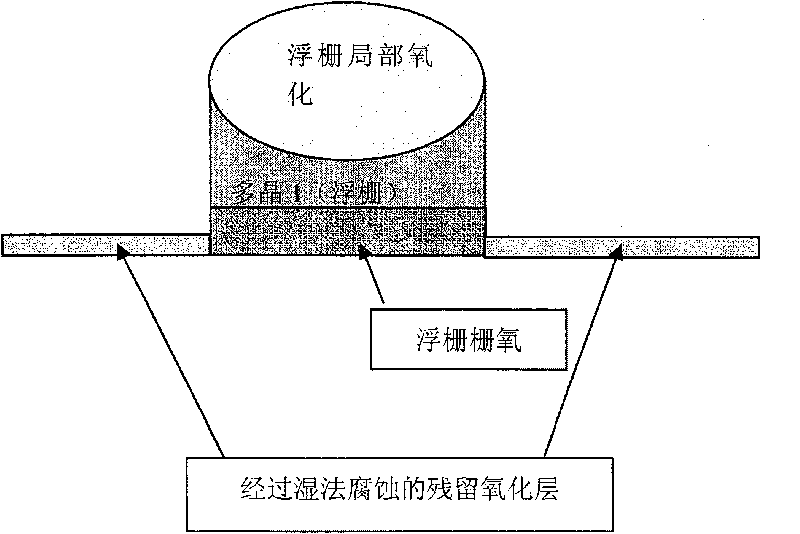

[0017] Reducing the thickness of the tunnel oxide layer, under the same working conditions, not only directly enhances the electric field strength during erasing, but also reduces the number of traps in the oxide layer, which is conducive to improving the erasing ability of the memory cell, thereby increasing its erasing and writing times . When the tunnel oxide thickness is reduced to , its erase and write times can reach 200,000 times.

[0018] However, the thickness of the high-voltage oxide layer must meet the withstand voltage requirements of the high-voltage transistor. Since flash memory uses a voltage as high as 12-14V, the total thickness of the high-voltage gate oxide layer needs to be greater than In order to ensure its normal operation and reliability requirements. In the current process in which the high-voltage gate oxide and the tunnel oxide layer are formed simultaneously, it is difficult to further reduce the thickness of the tunnel oxide layer.

[0019]...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com