Integrated circuit package structure and anti-warp substrates

An integrated circuit and structural technology, applied in circuits, electrical components, electrical solid devices, etc., can solve the problems affecting cutting efficiency, general products have no structure, inconvenience, etc., and achieve the effect of enhancing structural strength and improving anti-warping performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

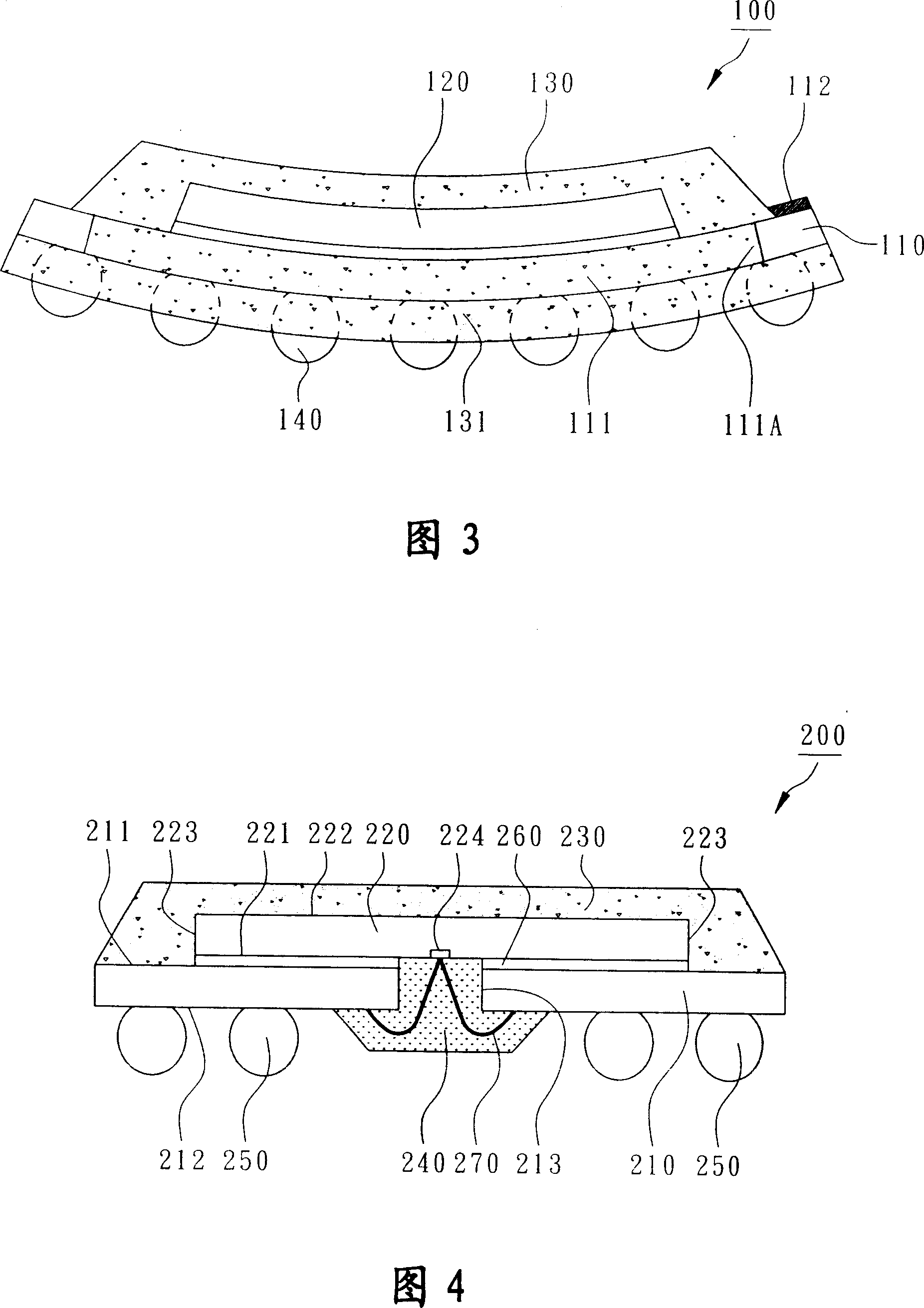

[0102] In order to further explain the technical means and effects that the present invention adopts to achieve the intended invention purpose, the specific implementation, structure, features and effects of the integrated circuit packaging structure proposed according to the present invention will be described below in conjunction with the accompanying drawings and preferred embodiments. , as detailed below.

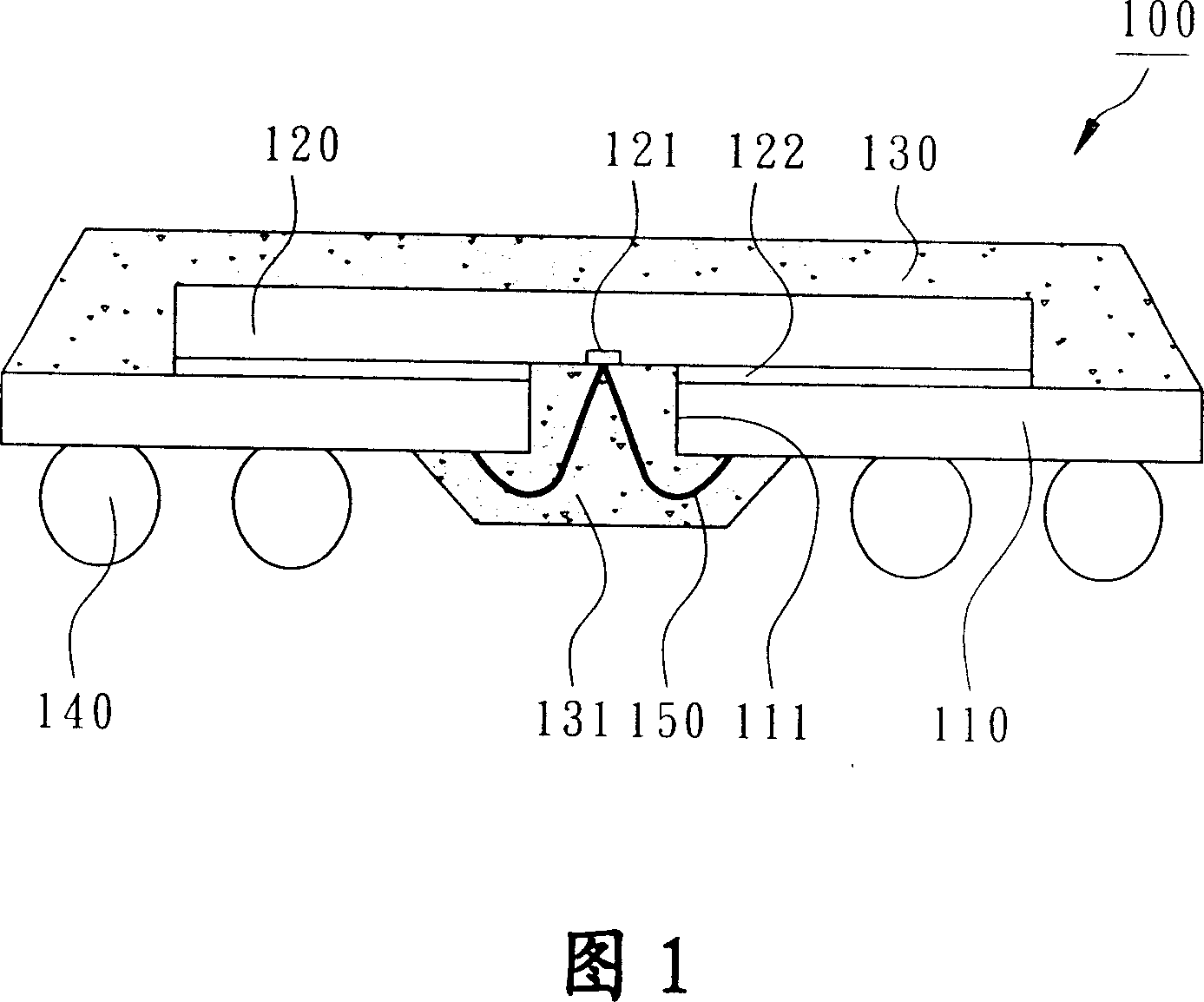

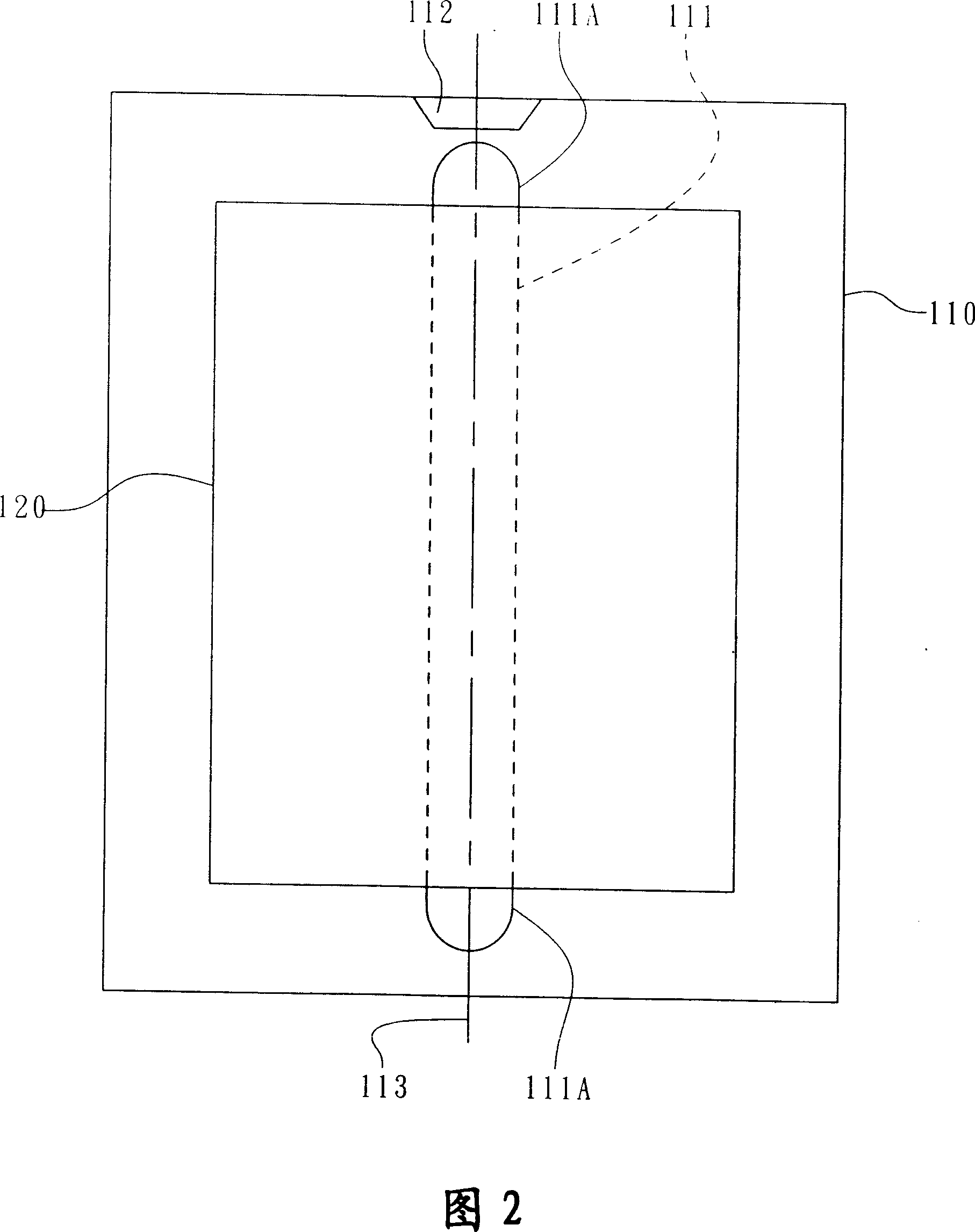

[0103] Please refer to FIG. 4 to FIG. 8 , which are related to the first specific embodiment of the present invention, which discloses an integrated circuit packaging structure. The integrated circuit packaging structure 200 can be a window type ball grid array package (Window BGA package), mainly including a substrate 210, a chip 220, a covering molding body 230, at least one reinforcing type molding body 240 and a plurality of external connections. Terminal 250.

[0104] The substrate 210 is used as an IC carrier board and has circuit patterns for electrical transmis...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Young's modulus | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com