Embedded heterogeneous polynuclear cache coherence method based on bus snooping

A heterogeneous multi-core, embedded technology, applied in memory systems, memory address/allocation/relocation, instruments, etc., can solve problems such as data inconsistency, L1 cache data inconsistency, data errors, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

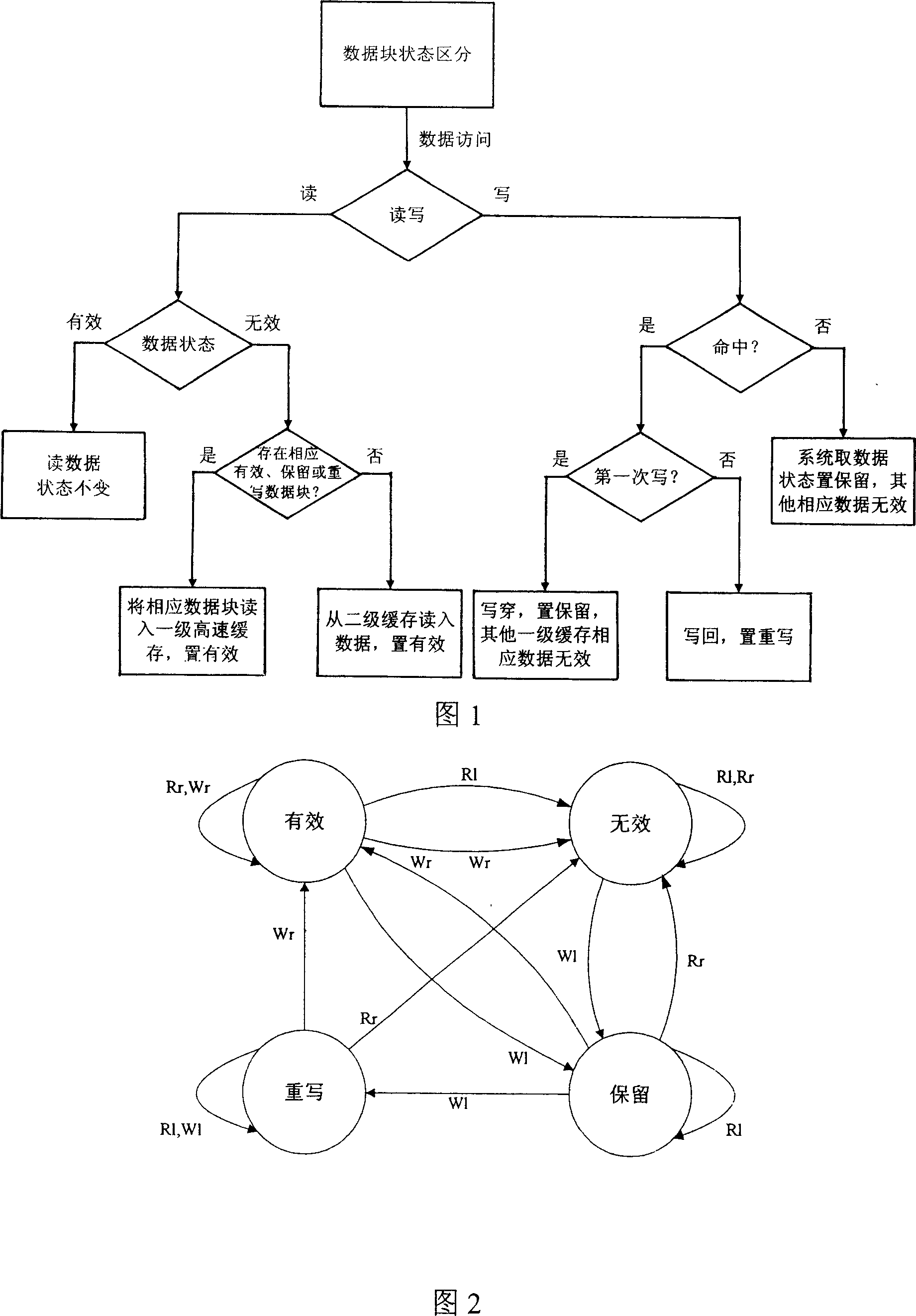

[0029] The specific implementation process of the present invention is shown in FIG. 1 .

[0030] Step 1: Data block status distinction

[0031] According to whether the data block in the read and write operation is the first write, the data block in the first-level cache is divided into four states:

[0032] "Valid": the first-level cache data block read from the second-level cache and consistent with the copy of the second-level cache;

[0033] "Invalid": not found in the first-level cache or the content of the data block in the first-level cache is "obsolete";

[0034] "Reserved": The data is only written once after being read from the L2 cache into the L1 cache, the copy in the L1 cache is consistent with the copy in the L2 cache, and it is a correct copy;

[0035] "Rewrite": the data block in the first-level cache has been written more than once, and it is the only correct data block. At this time, the data block in the second-level cache is not a correct data block eit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com