Method and circuit for detecting a fault in a clock signal for microprocessor electronic devices including memory elements

a clock signal and microprocessor technology, applied in the field of circuits for detecting irregularities in clock signals of electronic devices, can solve problems such as malfunctions during normal use, unusable effects of devices, and failure to correctly reset new devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

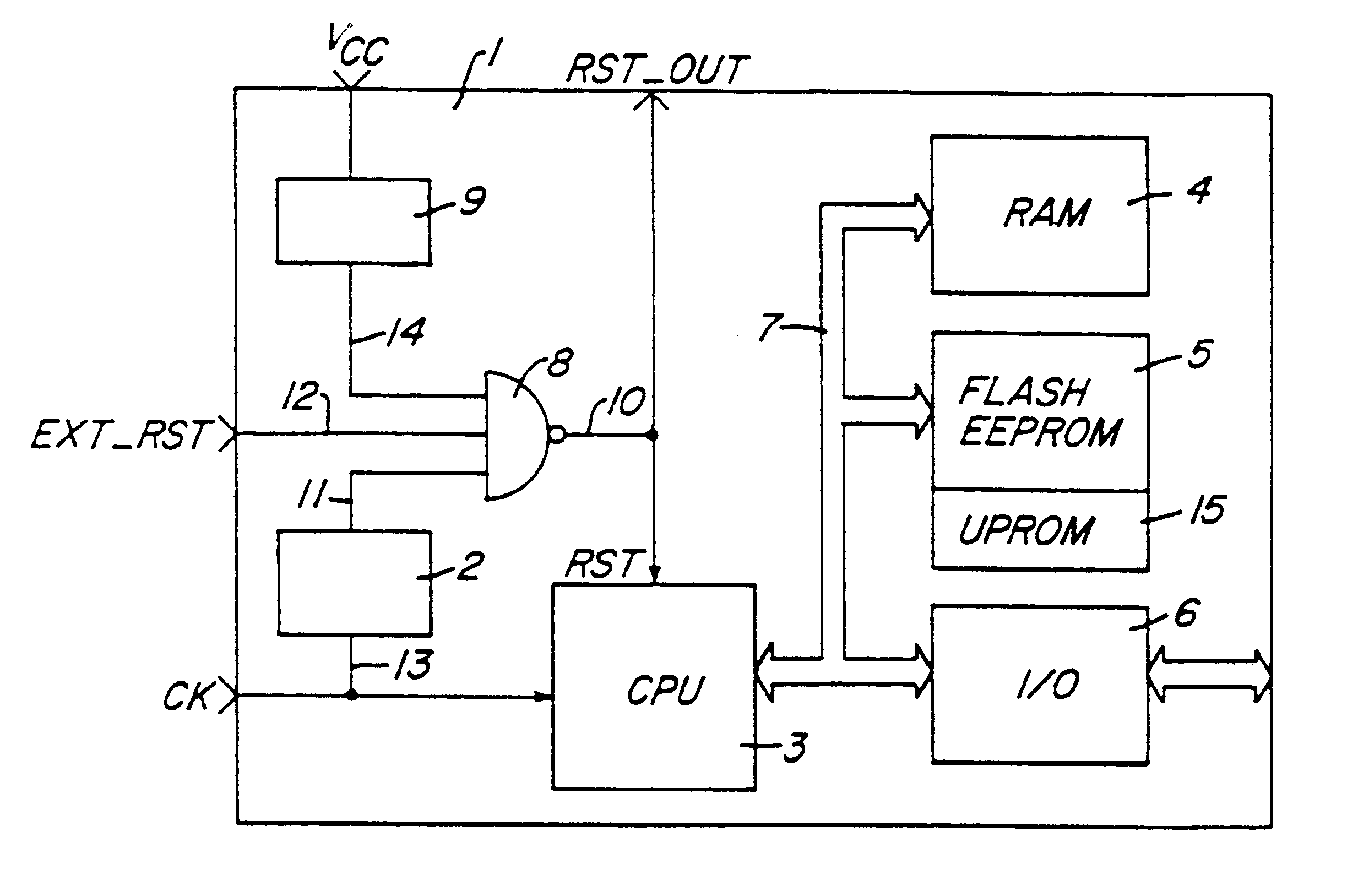

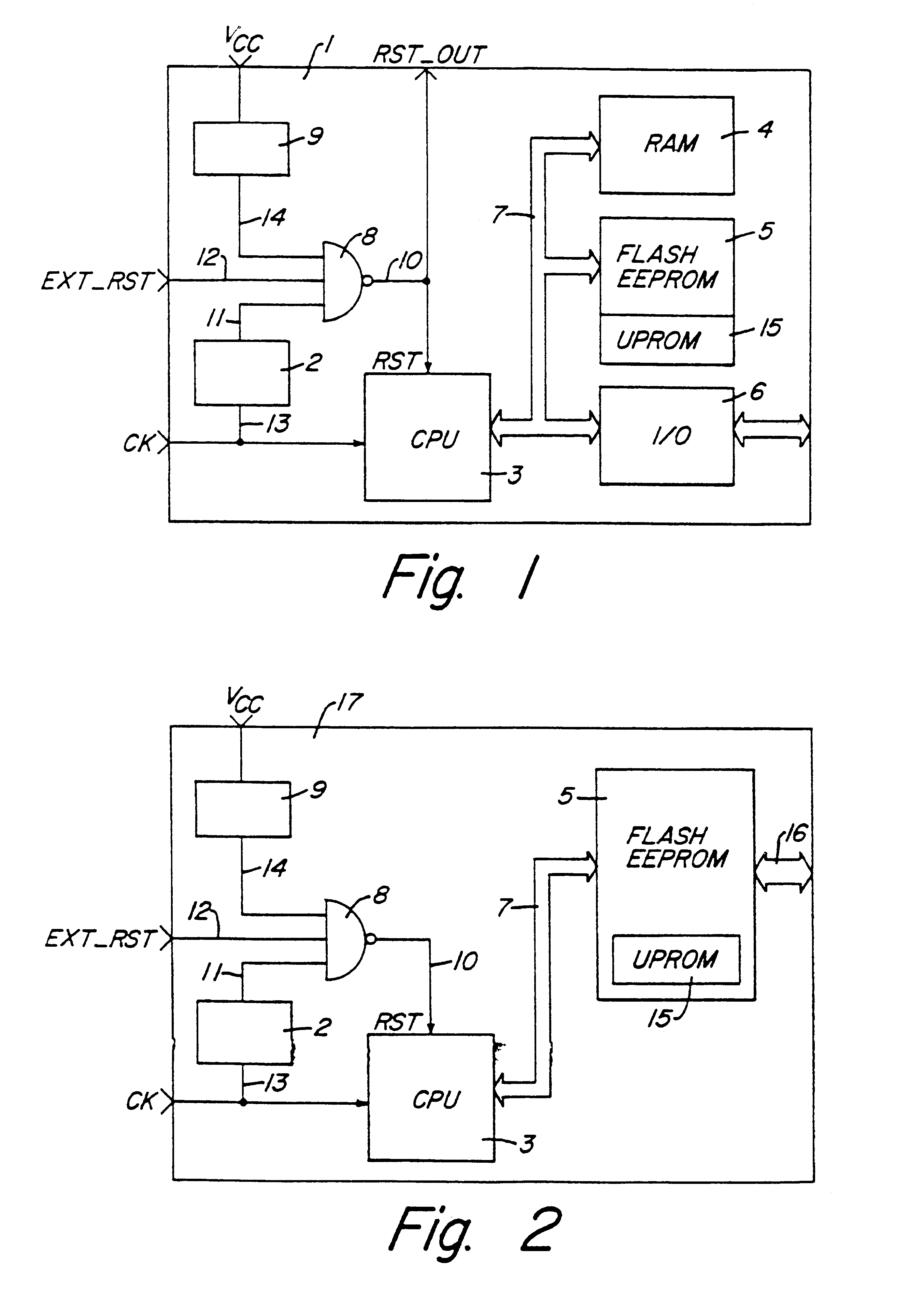

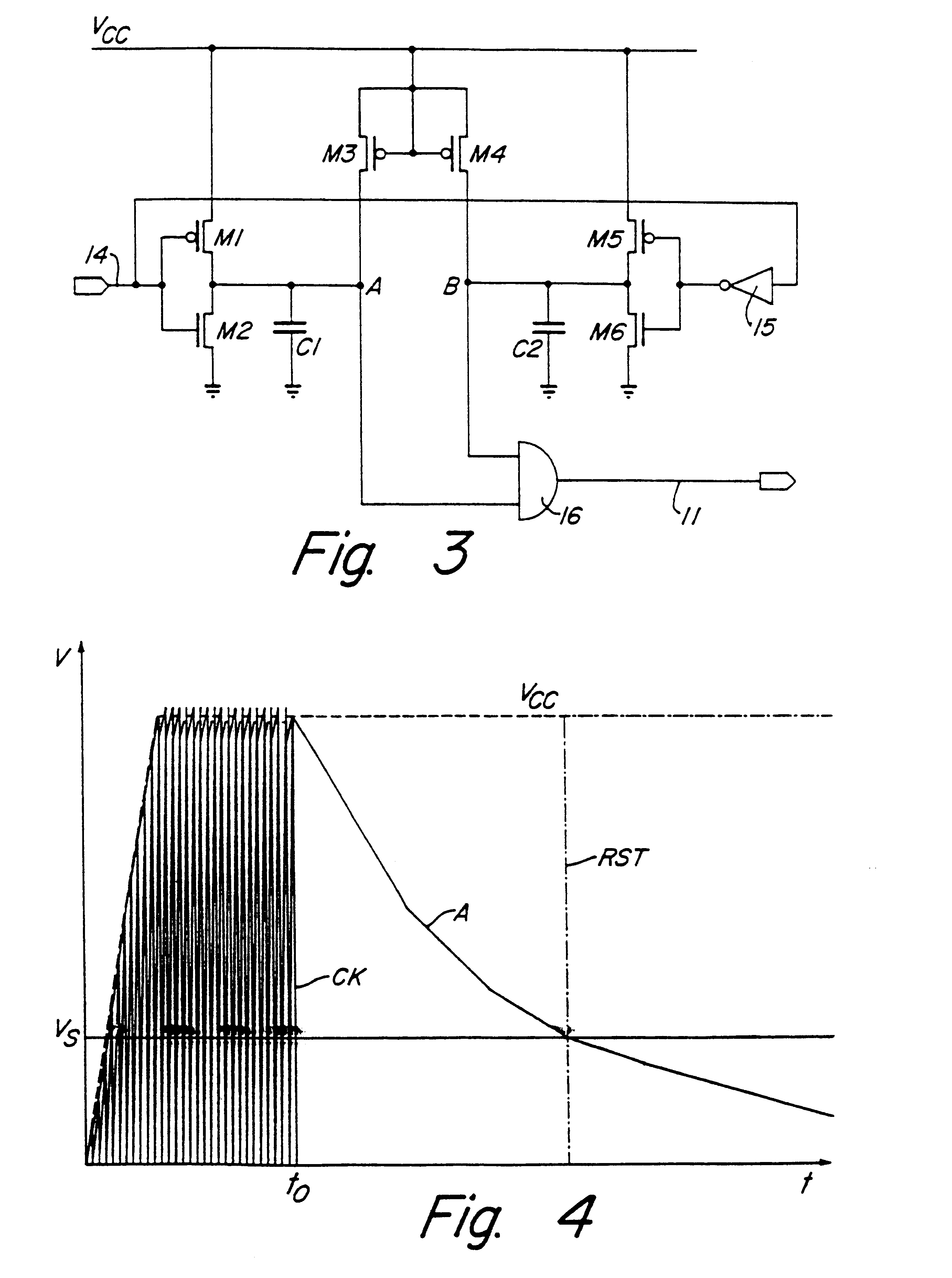

With reference to the figures reference number 1 indicates as a whole and schematically a first electronic device while said microcontroller comprises in a single semiconductor chip a microprocessor 3, a non-volatile memory matrix 5, a volatile memory matrix (RAM) 4, input and output ports 6 and some circuit blocks 2, 8 and 9 designed to generate a reset signal.

Blocks 3, 4, 5 and 6 communicate with each other through a group of electrical connections 7 known as data and address busses with which they are interfaced.

The non-volatile memory matrix 5 is electrically programmable and erasable and can be the EEPROM or the FLASH EEPROM type and is used for permanently memorizing the sequence of instructions for the microprocessor 3. This memory contains a certain number of cells of UPROM (Unerasable and Programmable Read Only Memory) 15 which is programmed by the manufacturer of the integrated circuit during testing of the device and subsequently is not visible to the user.

The volatile me...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com