Vertical memory device and method of manufacturing the same

a technology of vertical memory and flash memory, which is applied in the direction of semiconductor devices, basic electric elements, electrical equipment, etc., can solve the problems of unstable response and variable memory window size of the flash memory device, and achieve the effect of increasing the density of the charge trap pattern and reducing cross talk

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029]Reference will now be made to some example embodiments, which are illustrated in the accompanying drawings, wherein like reference numerals may refer to like components throughout.

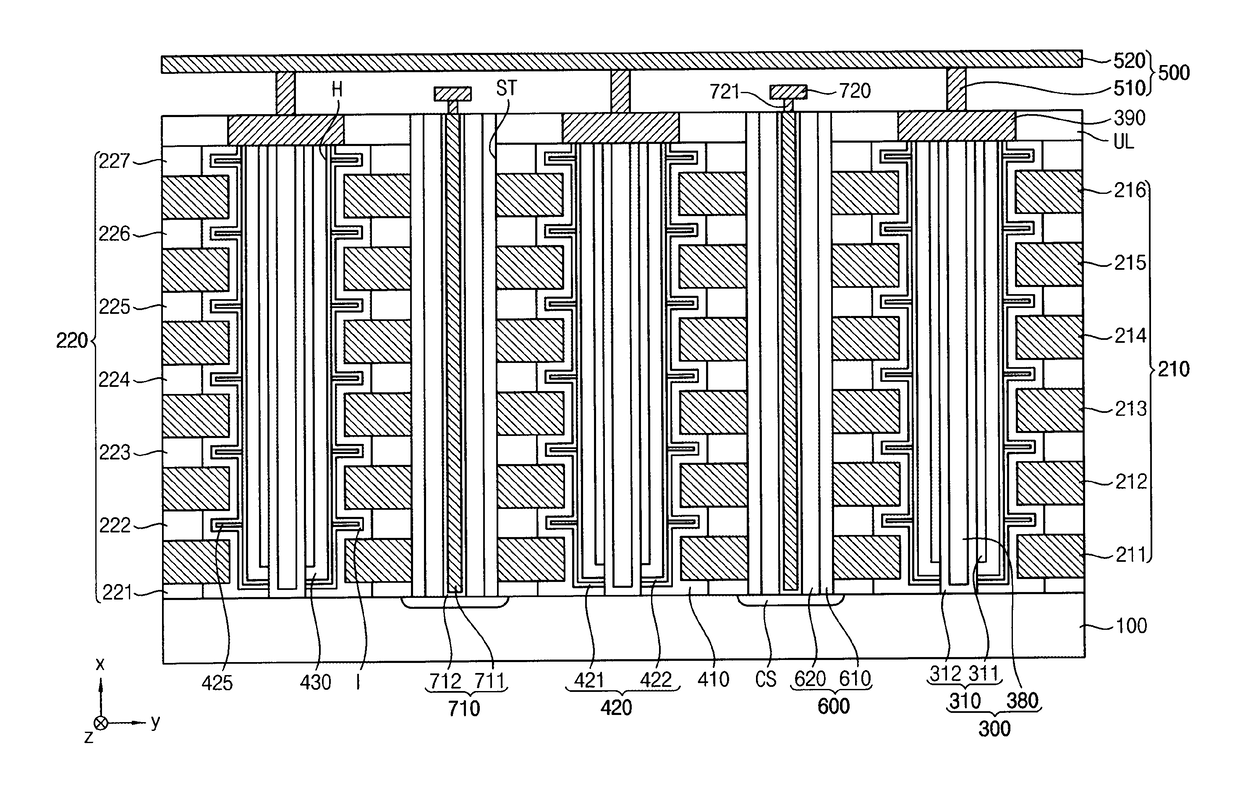

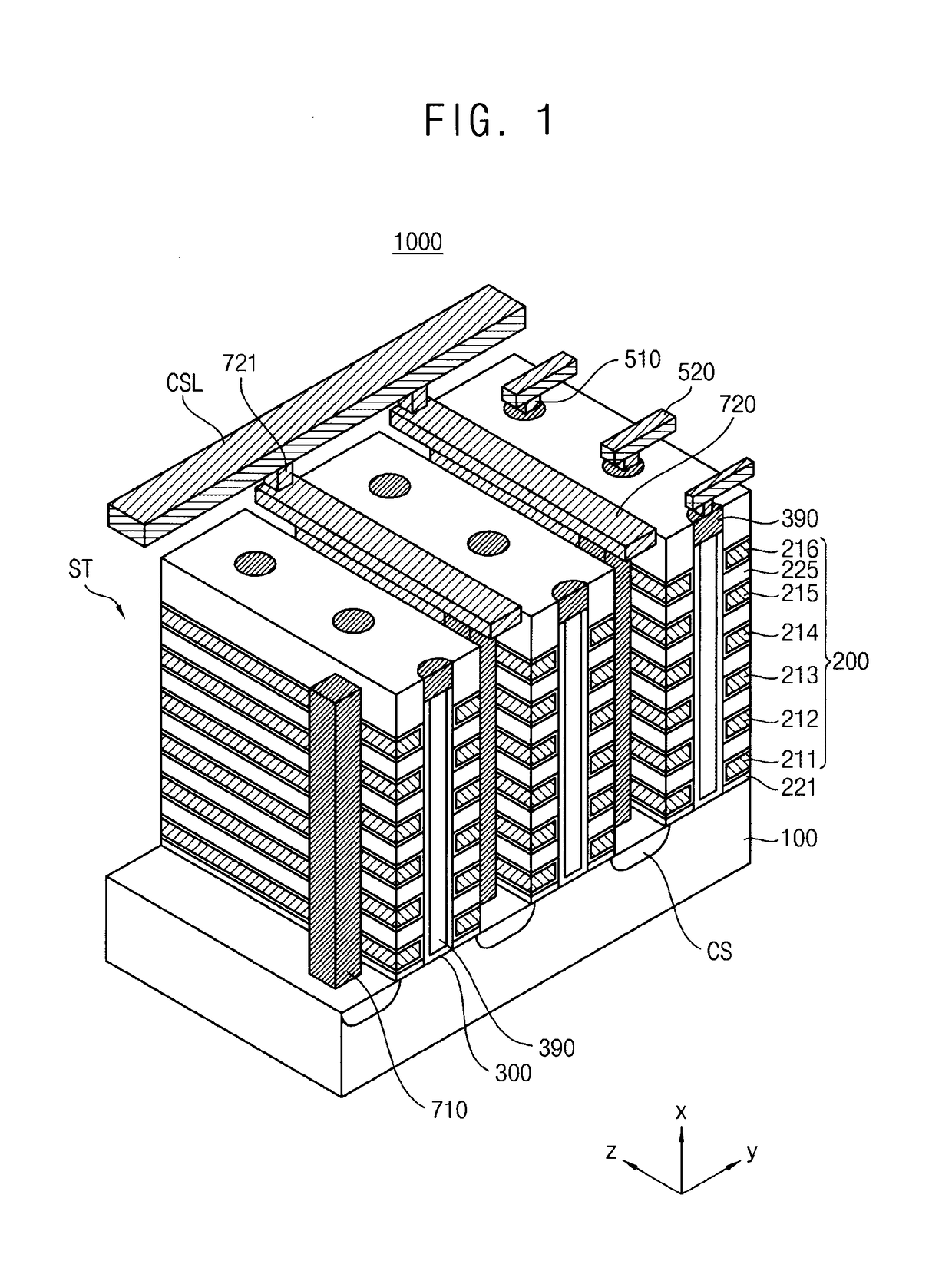

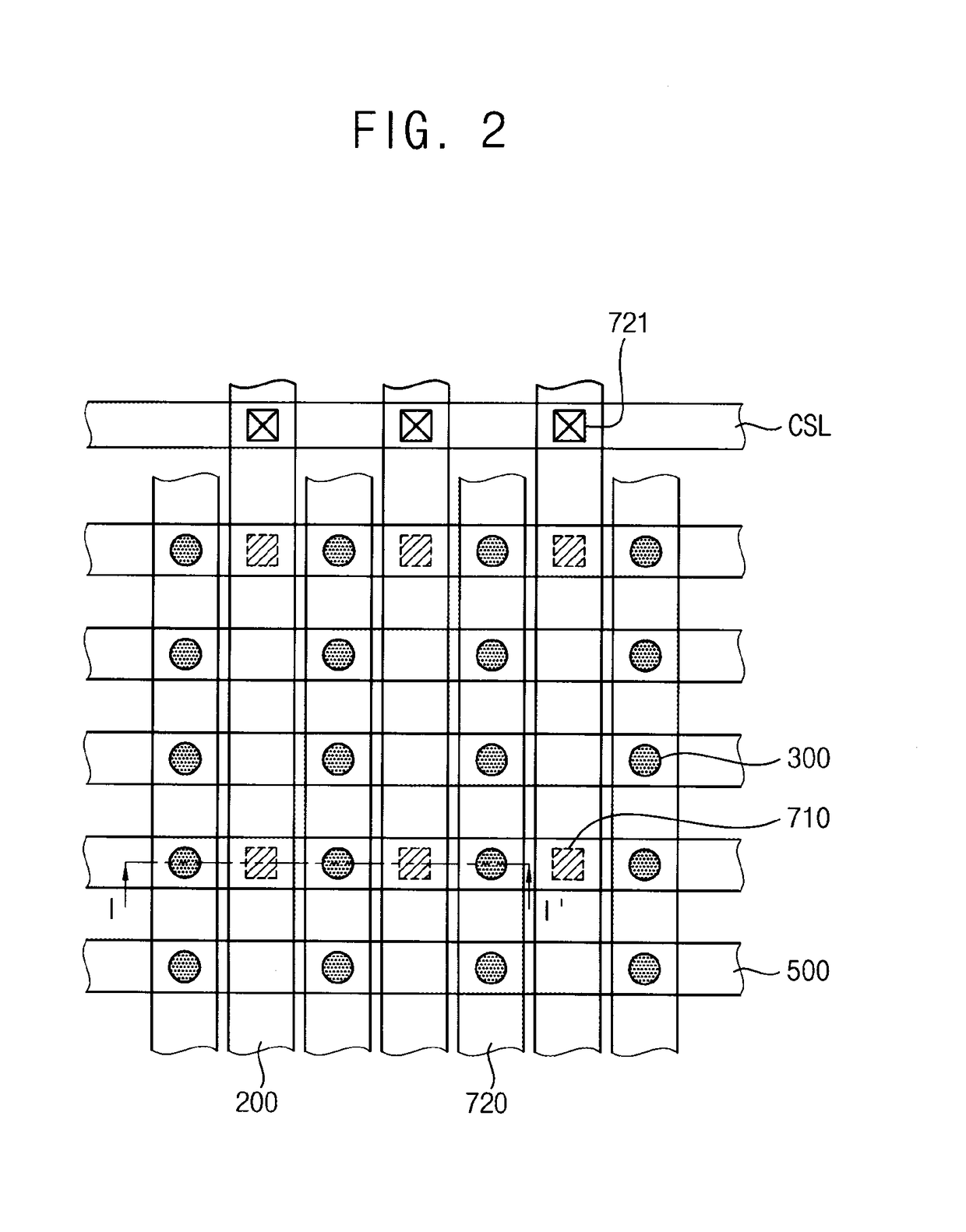

[0030]FIG. 1 is a perspective view illustrating a vertical non-volatile memory device in accordance with some example embodiments of inventive concepts, and FIG. 2 is a plan view illustrating the vertical non-volatile memory device shown in FIG. 1. FIG. 3 is a cross sectional view illustrating the vertical non-volatile memory device shown in FIG. 1 cut along a line I-I′ of FIG. 2. FIG. 4 is an enlarged view of a portion A of FIG. 3.

[0031]Referring to FIGS. 1 to 4, the vertical non-volatile memory device 1000 in accordance with some example embodiments of inventive concepts may include a gate stack structure 200 having conductive structures and insulation interlayer structures that are alternately stacked in a first direction x on a substrate 100, an active column 300 penetrating through the gate stac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com