Schottky diode integrated into LDMOS

a metal oxide semiconductor and diode technology, applied in the direction of semiconductor devices, electrical apparatus, transistors, etc., can solve the problems of high dynamic loss of ldmos, slow reverse recovery time, and loss of conduction loss in the inherent body diodes of the device, so as to reduce forward conduction loss, reduce leakage, and increase the safe operating area of ldmos

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018]The present invention provides an LDMOS device with integrated Schottky diode.

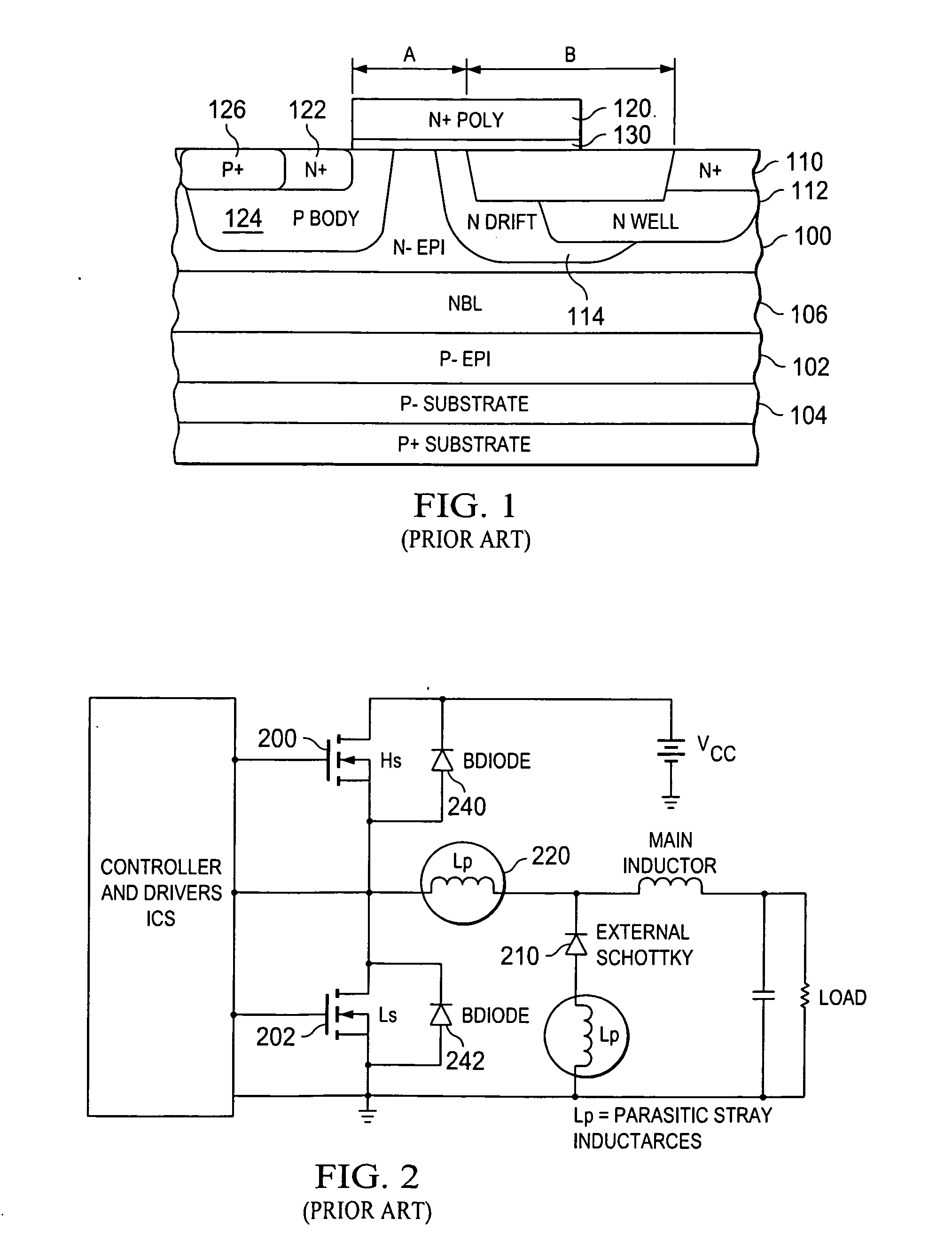

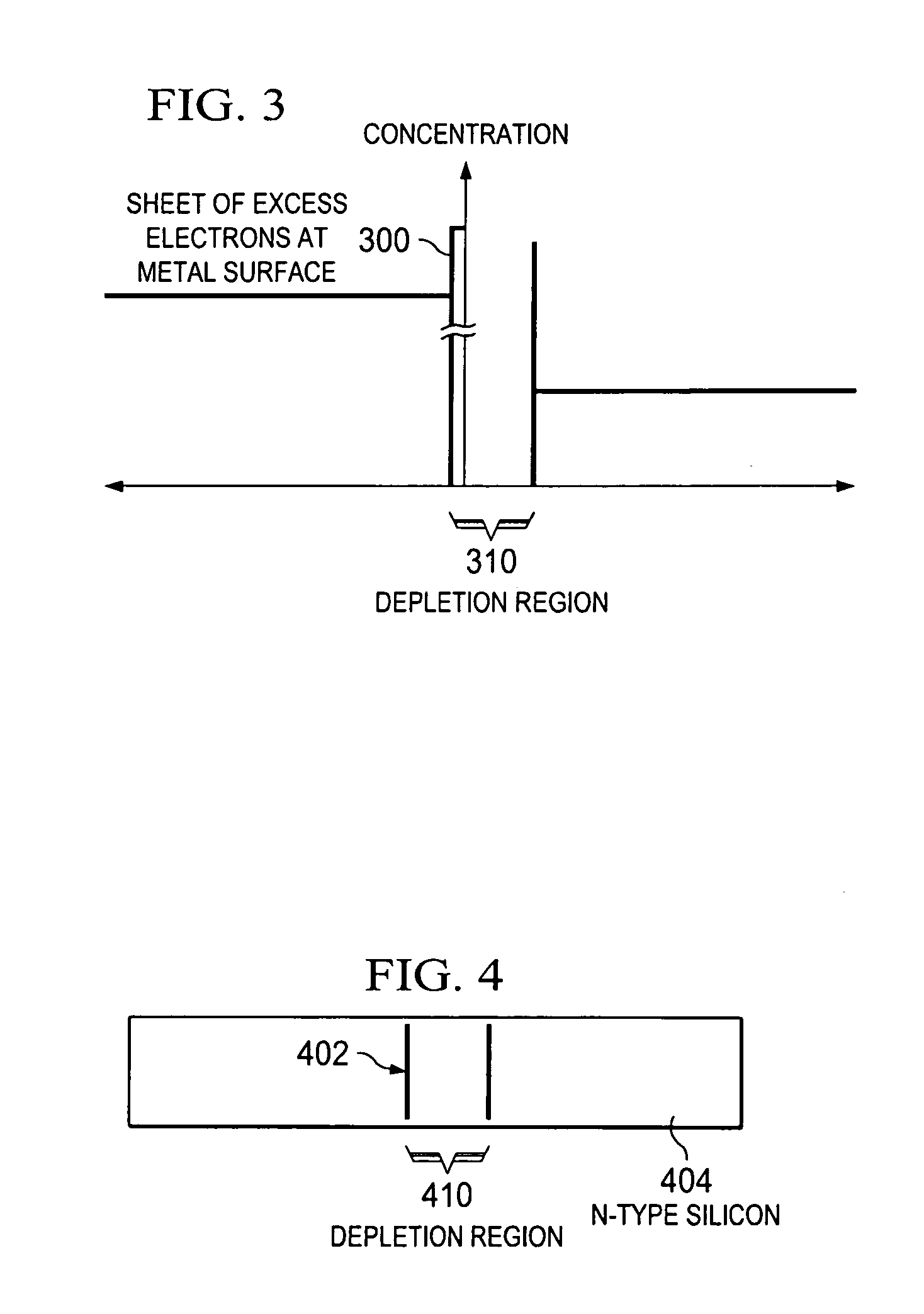

[0019]Schottky diodes are formed when a metal plate is brought into contact with lightly doped n-type silicon. As depicted in FIGS. 2 and 3, this creates a high concentration of electrons 300 at the surface 402 of the metal plate where it contacts the n-type silicon 404, and a depletion region 310, 410 between the metal plate and the n-type silicon, which shows the electron concentration across the Schottky diode. This provides the Schottky diode with a forward breakdown voltage Vf of about 0.3V compared to about 0.7V for a p-n diode formed between p-type silicon and n-type silicon. The benefits of a lower Vf are realized when the LDMOS is implemented in a circuit such as the buck converter of FIG. 2.

[0020]FIG. 5 shows the typical waveforms for a synchronous buck converter. As can be seen by comparing the voltage waveform on the gate of the high side LDMOS 100 (curve 500) with the voltage waveform on...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com