Semiconductor device and method of manufacturing the same

a semiconductor and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical equipment, etc., can solve problems such as product stress at a problematic level, bump crack or chip crack, etc., and achieve the effect of reducing stress and stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0029]A first embodiment according to the present invention will be described with reference to the drawings. FIG. 4 is a cross-sectional view showing a semiconductor device according to the present embodiment.

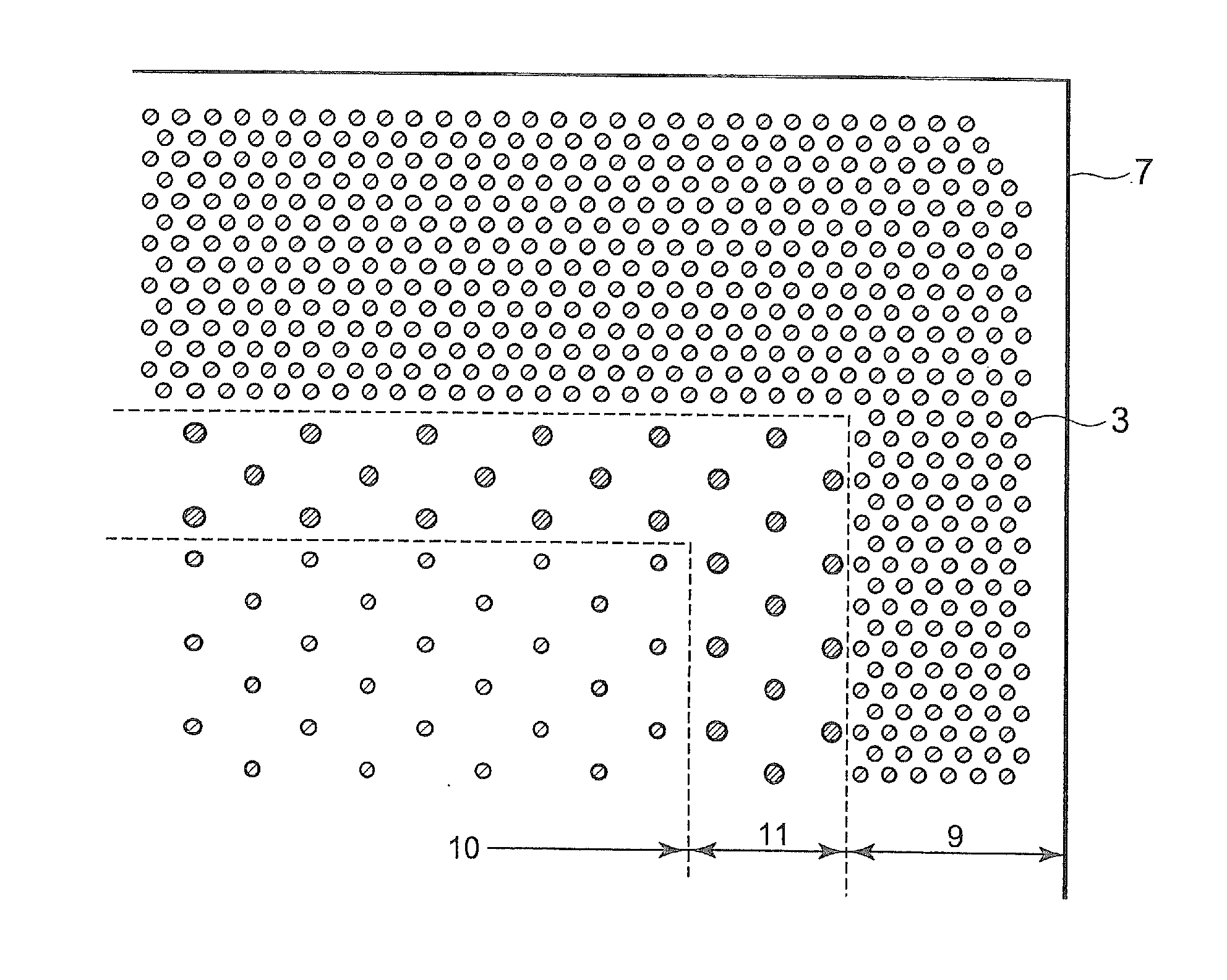

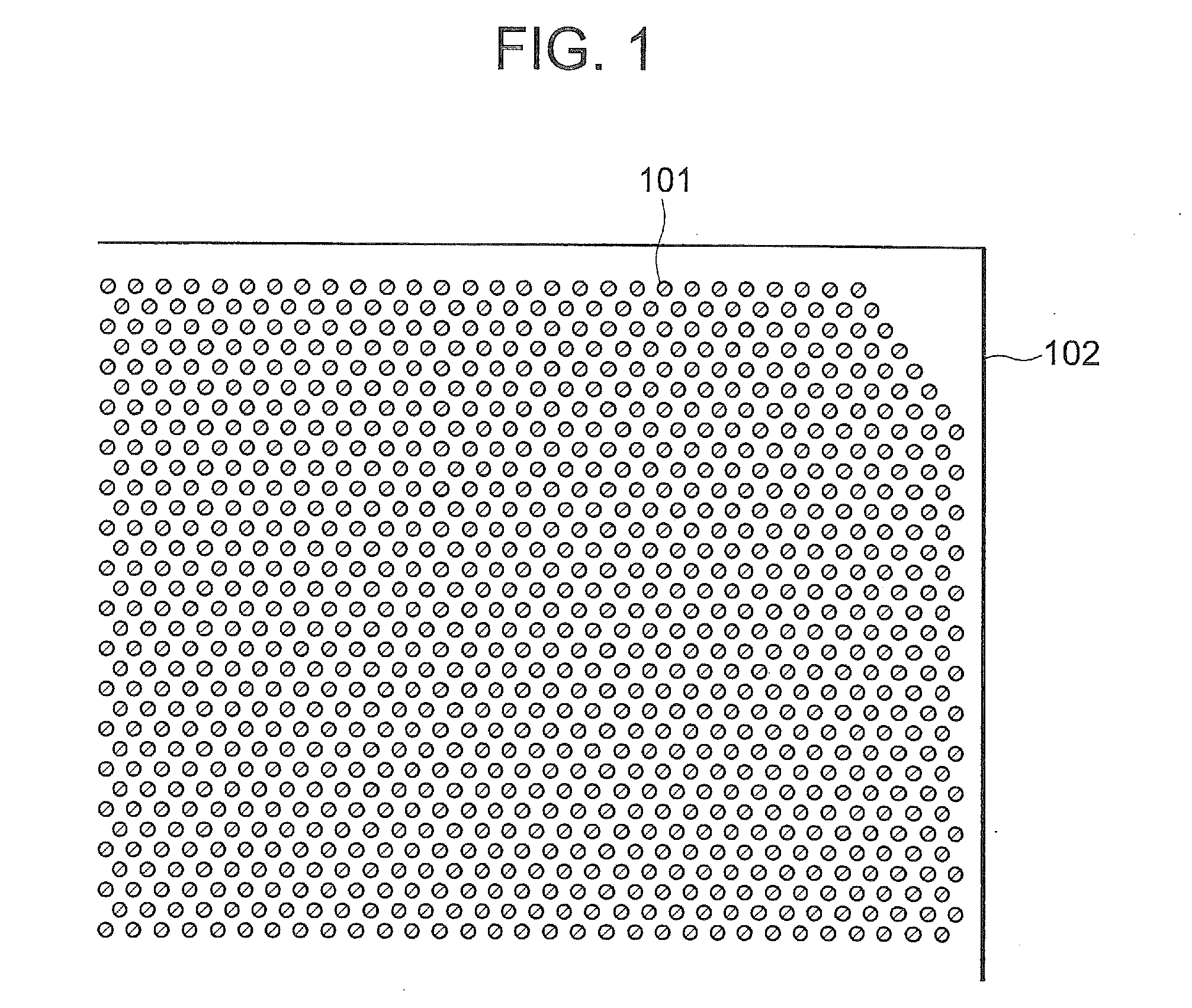

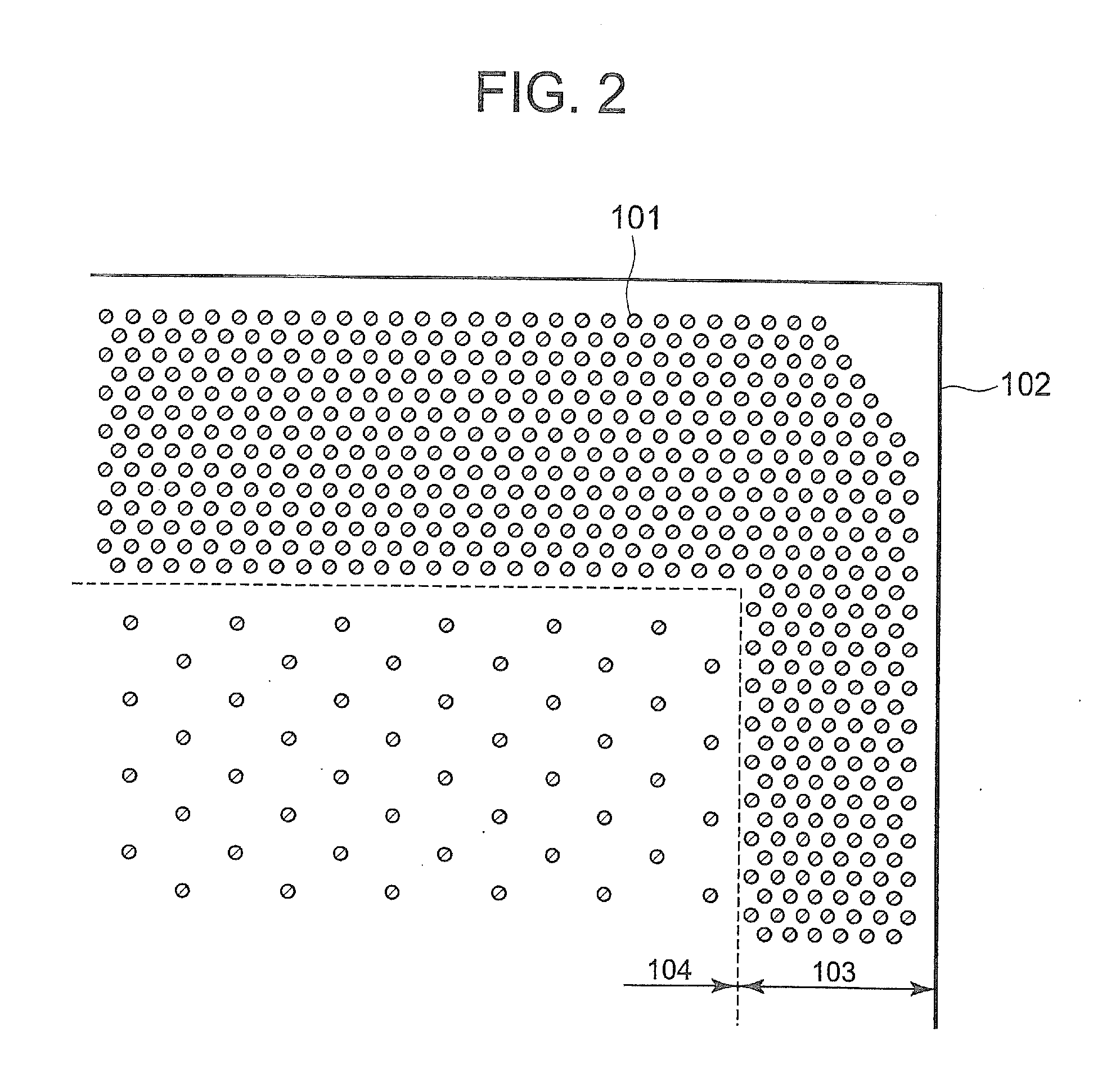

[0030]As shown in FIG. 4, the semiconductor device of the present embodiment includes a wiring board and a semiconductor chip 13. The wiring board 1 has a chip mounting surface 12. On the chip mounting surface 12, multiple electrode terminals 5 are formed as an electrode terminal group. Meanwhile, the semiconductor chip 13 includes a chip substrate 2 having a semiconductor integrated circuit formed thereon. The chip substrate 2 is provided with a bump formation surface 7. Multiple bumps 3 are formed on the bump formation surface 7 as a bump 3 group. The semiconductor chip 13 is mounted on the wiring board 1 so that the bump formation surface 7 would face the chip mounting surface 12. An arrangement pattern of the bumps 3 on the bump formation surface 7 is the same as an arrang...

second embodiment

[0044]Next, a second embodiment will be described. FIG. 8 shows a bump formation surface 7 of a semiconductor device according to the second embodiment. In the present embodiment, the size and the arrangement of bumps 3 in a third region 11 are different from those in the first embodiment. The other points may be the same as the first embodiment, and thus the detailed description thereof is omitted here.

[0045]In the present embodiment, as in the case of the first embodiment, the region of the third region 11 having the bumps 3 arranged thereon has an area density (third density) which is higher than a second density and is lower than a first density. However, in the present embodiment, the number of the bumps 3 arranged per unit area in the third region 11 is the same as that in the second region 10. Meanwhile, the size of each of the bumps 3 arranged in the third region 11 is larger than the size of each of the bumps 3 arranged in the first region 9 and the second region 10. Note t...

third embodiment

[0050]Next, a third embodiment of the present invention will be described. FIG. 10 shows a bump formation surface 7 of a semiconductor device according to the third embodiment. In the present embodiment, a bump group provided on the bump formation surface 7 includes actual bumps 3-1 and dummy bumps 3-2. The other points maybe the same as the above-described embodiments, and thus the detailed description thereof is omitted here.

[0051]The actual bumps 3-1 are bumps used for electrical connection between a semiconductor chip 13 and a wiring board 1. On the other hand, the dummy bumps 3-2 are provided to control the area density of a region where the bumps are arranged, and are not used for the electrical connection between the semiconductor chip 13 and the wiring board 1.

[0052]According to the present embodiment, the stress can be reduced by the same effects as the above-described embodiments. In addition, the area density of a region where the bumps 3 are arranged can be controlled by...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com