Method and apparatus for direct backup of memory circuits

a memory circuit and state information technology, applied in the field of circuits and methods to backup state information, can solve the problems of consuming an inordinate amount of time, affecting the efficiency of state saving techniques, and defeating the purpose of power gating in an integrated circui

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

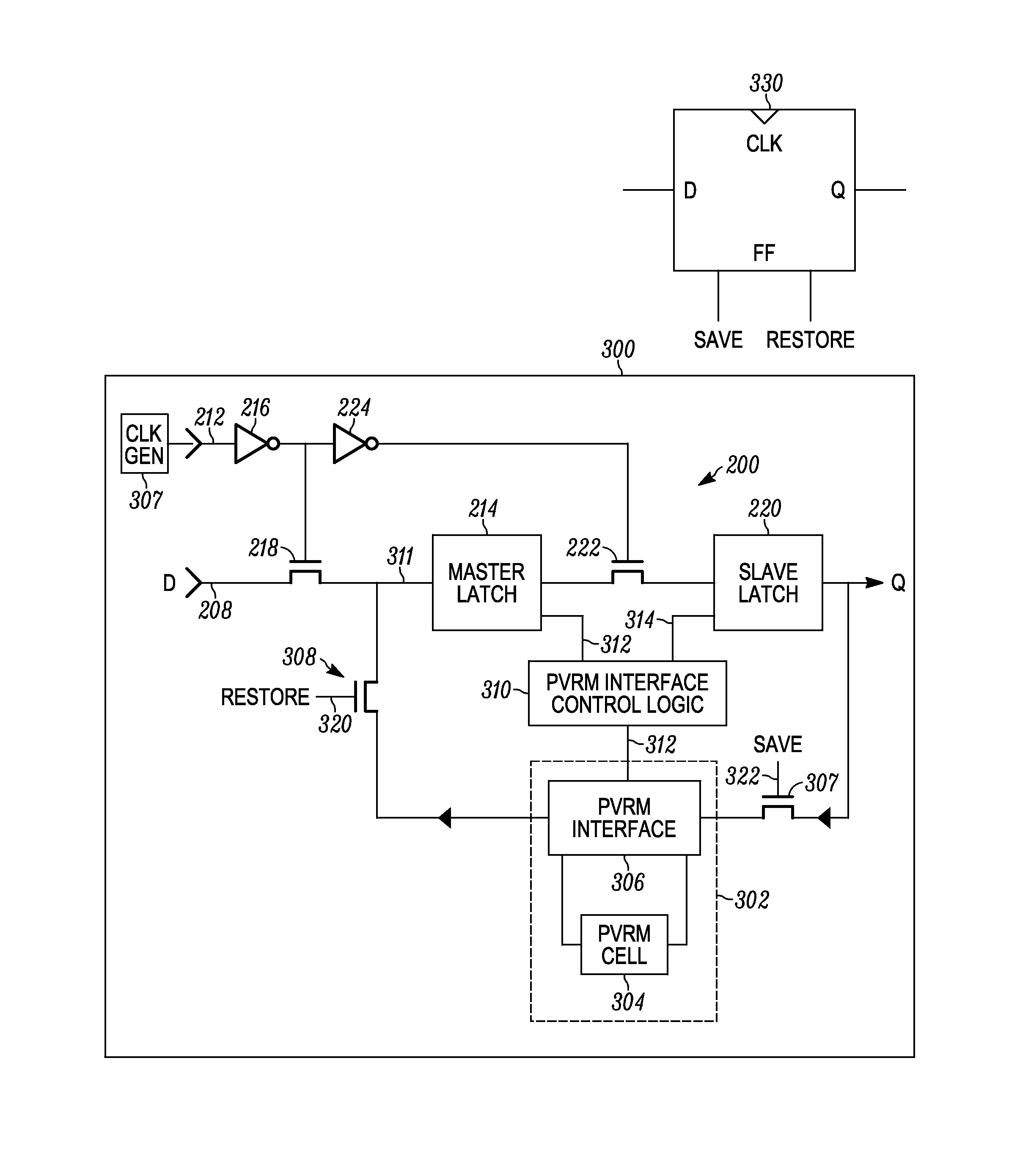

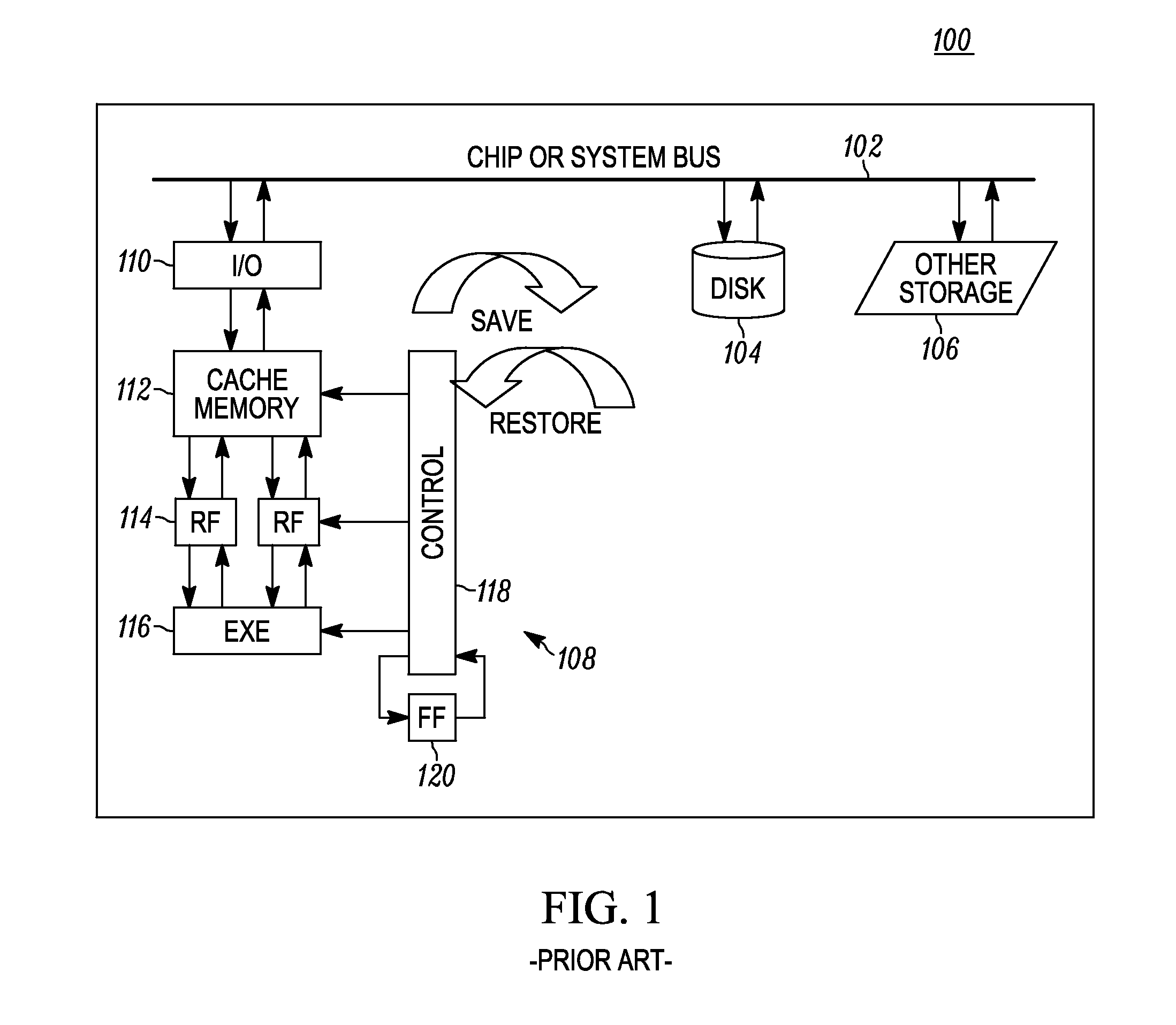

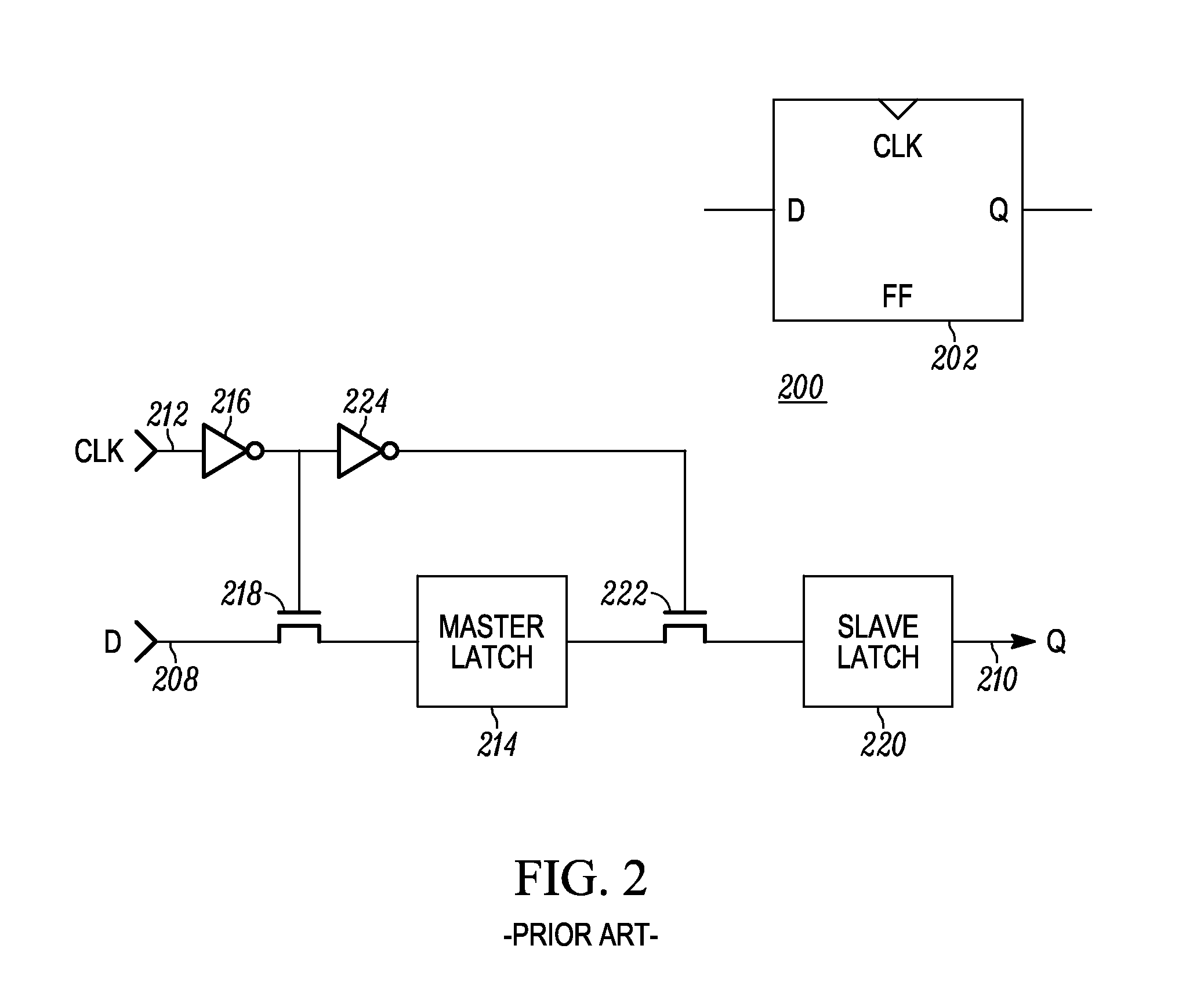

[0016]Briefly, an integrated circuit employs at least one active memory circuit and at least one memory state backup circuit wherein at least one memory state backup circuit includes at least one passive variable resistance memory (PVRM) cell and at least one passive variable resistance memory cell interface that are used to backup data from the active memory circuit to the PVRM cell. Data is then placed back into the active memory circuit from the PVRM cell during a restore operation. The PVRM cell interface is operative to read the PVRM cell in response to a restore signal. PVRM cell interface control logic is operative to remove power to the PVRM cell after backup of the data to the PVRM cell from the active memory circuit. A PVRM cell (e.g., a bit cell) is added to each memory circuit that stores state information on an integrated circuit. At the point of power gating the memory circuit, the data therein is transferred from the volatile section of the active memory circuit into ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com