Semiconductor device and method of fabricating the same

a semiconductor chip and semiconductor technology, applied in the field of semiconductor chips, can solve the problems of increasing affecting the reliability of the portion, and unable to meet the requirements of the application, so as to prevent the crack, and reduce the deformation of the semiconductor chip

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

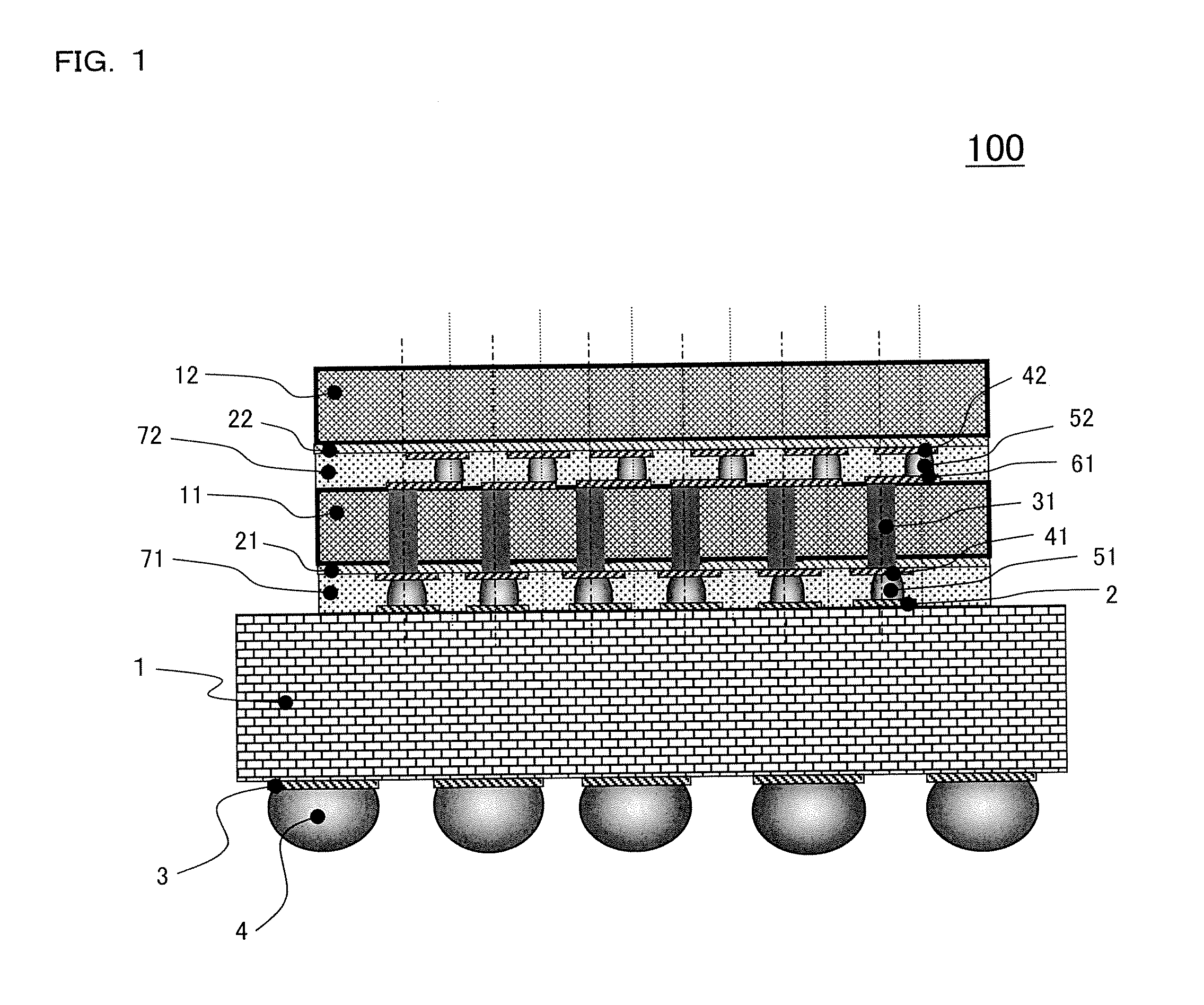

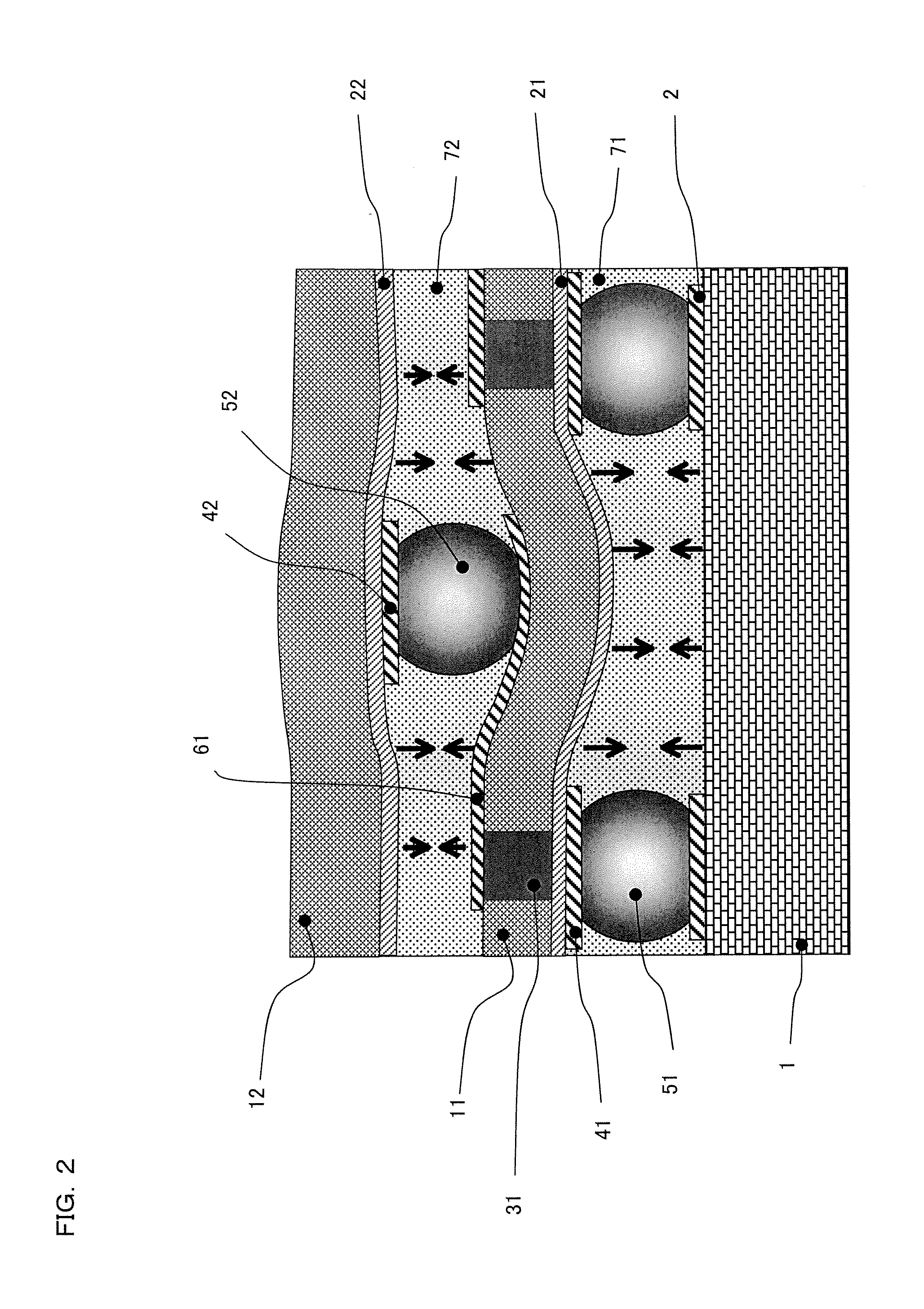

[0100]A structure of a semiconductor device according to a first embodiment of the present invention is basically the same as that of the semiconductor device 1000 according to the prior art shown in FIGS. 28 and 29. The semiconductor device according to the first embodiment of the present invention is the same as the semiconductor device 1000 according to the prior art except for arrangement positions of a through via, an electrode pad and a bump. In the semiconductor device 1000 according to the prior art, a position at which a through via, an electrode pad and a bump are arranged on one semiconductor chip is the same as a position at which the above three components are arranged on another semiconductor chip. In contrast, in the semiconductor device according to the first embodiment of the present invention, a position at which a through via, an electrode pad and a bump are arranged on one semiconductor chip is shifted from a position at which the above three components are arran...

second embodiment

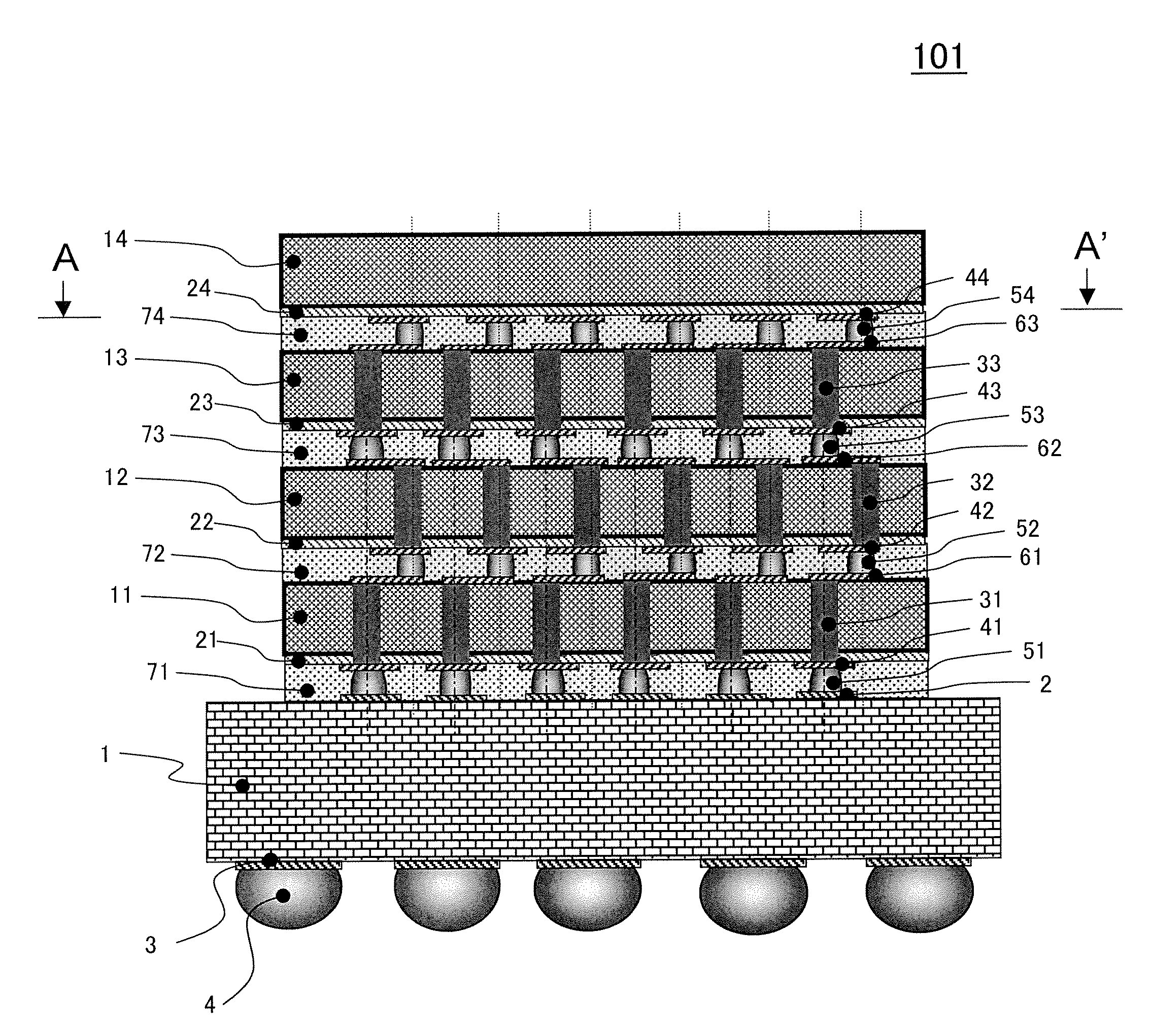

[0117]A structure of the semiconductor device according to a second embodiment of the present invention is basically the same as that according to the first embodiment of the present invention. Specifically, positions at which through vias are formed on each semiconductor chip are different between the first and second embodiments. In the semiconductor device according to the first embodiment of the present invention, on the circuit element surface of each of the semiconductor chips stacked in multi-layers, the electrode pad is arranged at a position at which the through via is formed so as to form the bump on the circuit element surface. In contrast, in the semiconductor device according to the second embodiment of the present invention, the bump is formed at a position shifted from a position at which the through via is formed on each of the semiconductor chips stacked in multi-layers. Hereinafter, the detailed structure of the semiconductor device according to the second embodime...

third embodiment

[0124]A structure of the semiconductor device according to a third embodiment of the present invention differs from that of the semiconductor device according to the first embodiment of the present invention in that in the semiconductor according to the third embodiment, a resin layer is additionally provided around the periphery of each bump.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com