Trench moseft with trench gates underneath contact areas of ESD diode for prevention of gate and source shortate

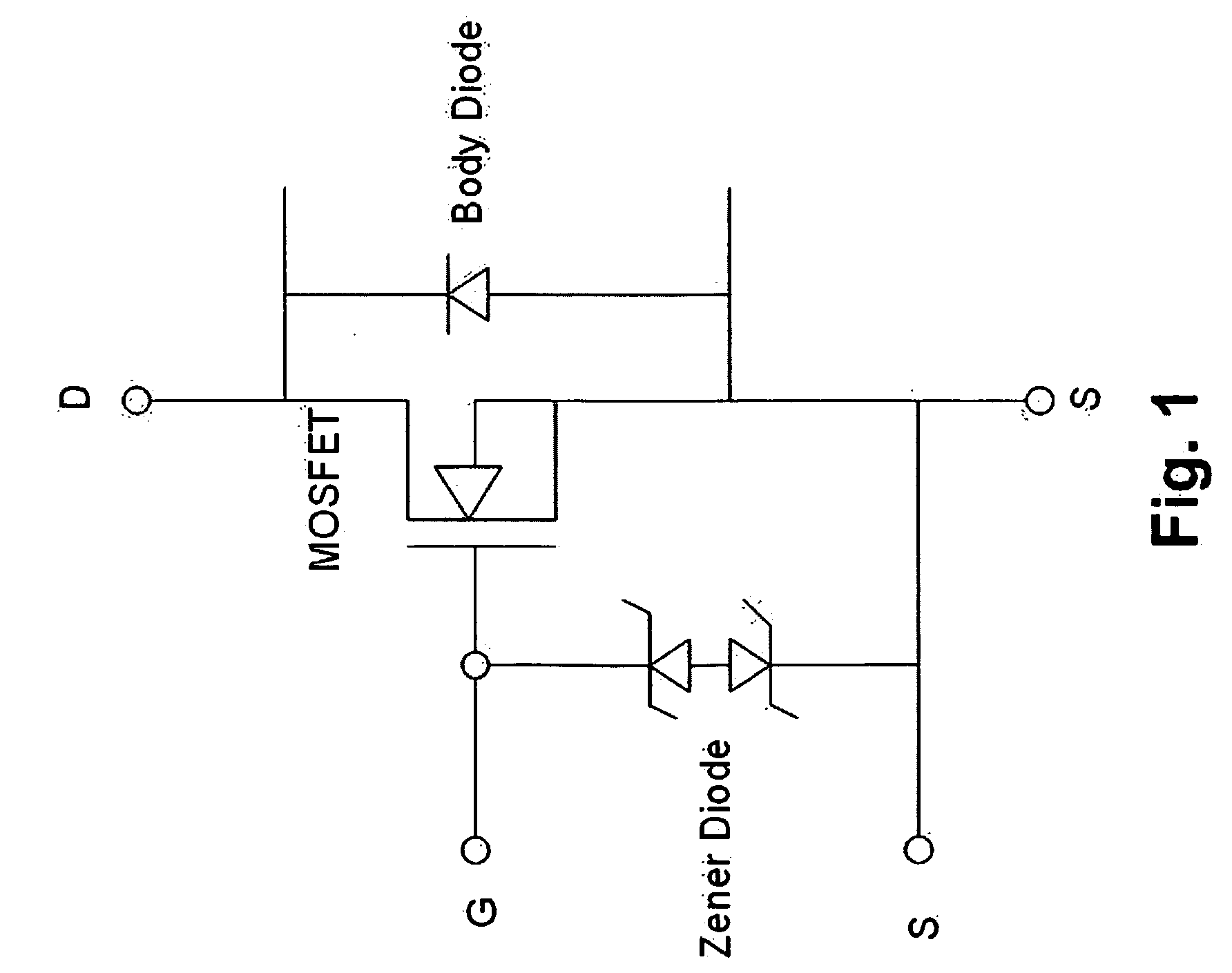

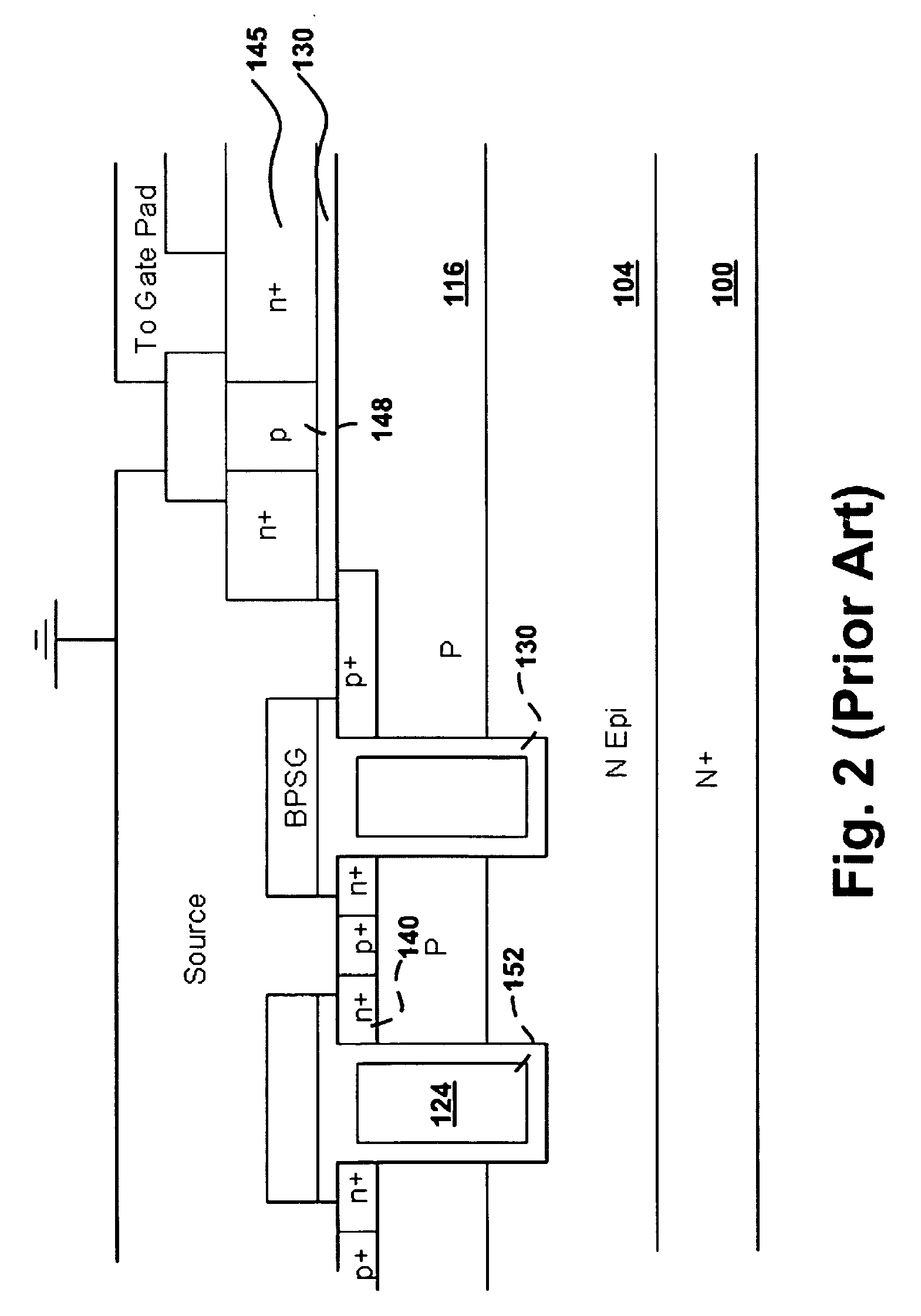

a technology of trench gates and moseft, which is applied in the field of cell structure, device configuration and fabrication process of moseft transistors, can solve the problems of permanent damage, dangerous conditions of dmos devices, and conventional technologies still have technical difficulties in dealing with electrostatic discharge (esd), so as to avoid esd shorting

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

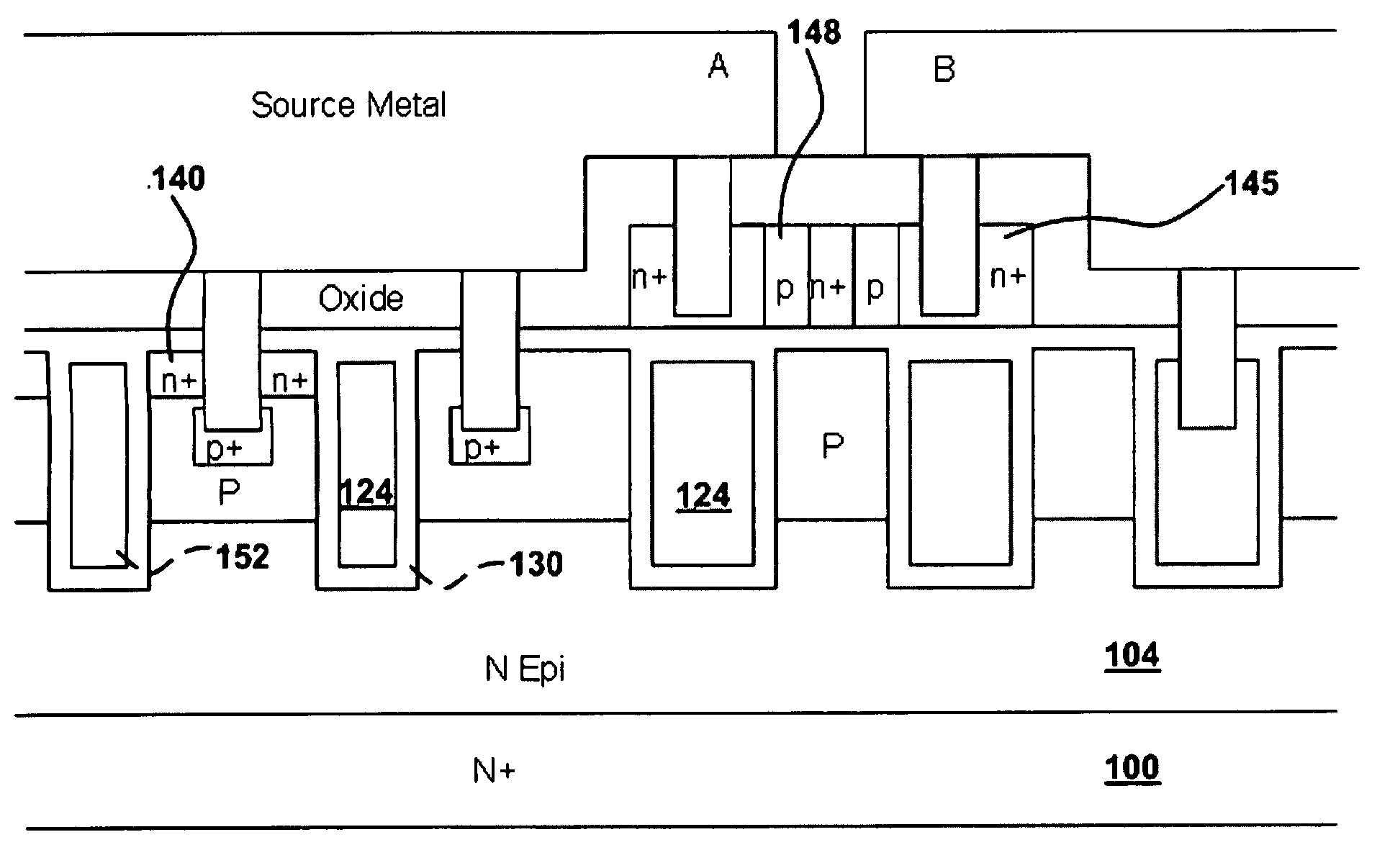

[0023]FIG. 4 illustrates the DMOS structure of this invention in cross-section. In FIG. 4, the ESD protection diode comprises cathodes 145 and anode 148. Trench gates are formed underneath contact areas of the ESD protection diode in order to resolve the problems discussed above. Besides these, the structure shown in FIG. 4 is advantageous because the source region 140 of the DMOS transistor and n+ cathode regions 145 of the Zener diode can be formed in the same mask and implantation steps, and all the trenches gate can be formed in the same mask and in the same step.

[0024]FIG. 5 illustrates the function of this invention when trenches are overetched. The ESD diode does not short to body-source as result of the trench gate underneath the contact area as buffer layer. The ESD diode will touch to the trench gates underneath without shorting source area.

[0025]FIGS. 6A-6G show a series of exemplary steps that are performed to form the inventive trench DMOS devices. In FIG. 6A, an N− dop...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com