Correction of incorrect cache accesses

a cache access and cache technology, applied in the field of data processing systems, can solve the problems of incorrect access to the cache, inability to uniquely identify the storage location, etc., and achieve the effect of reducing the latency of memory access

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

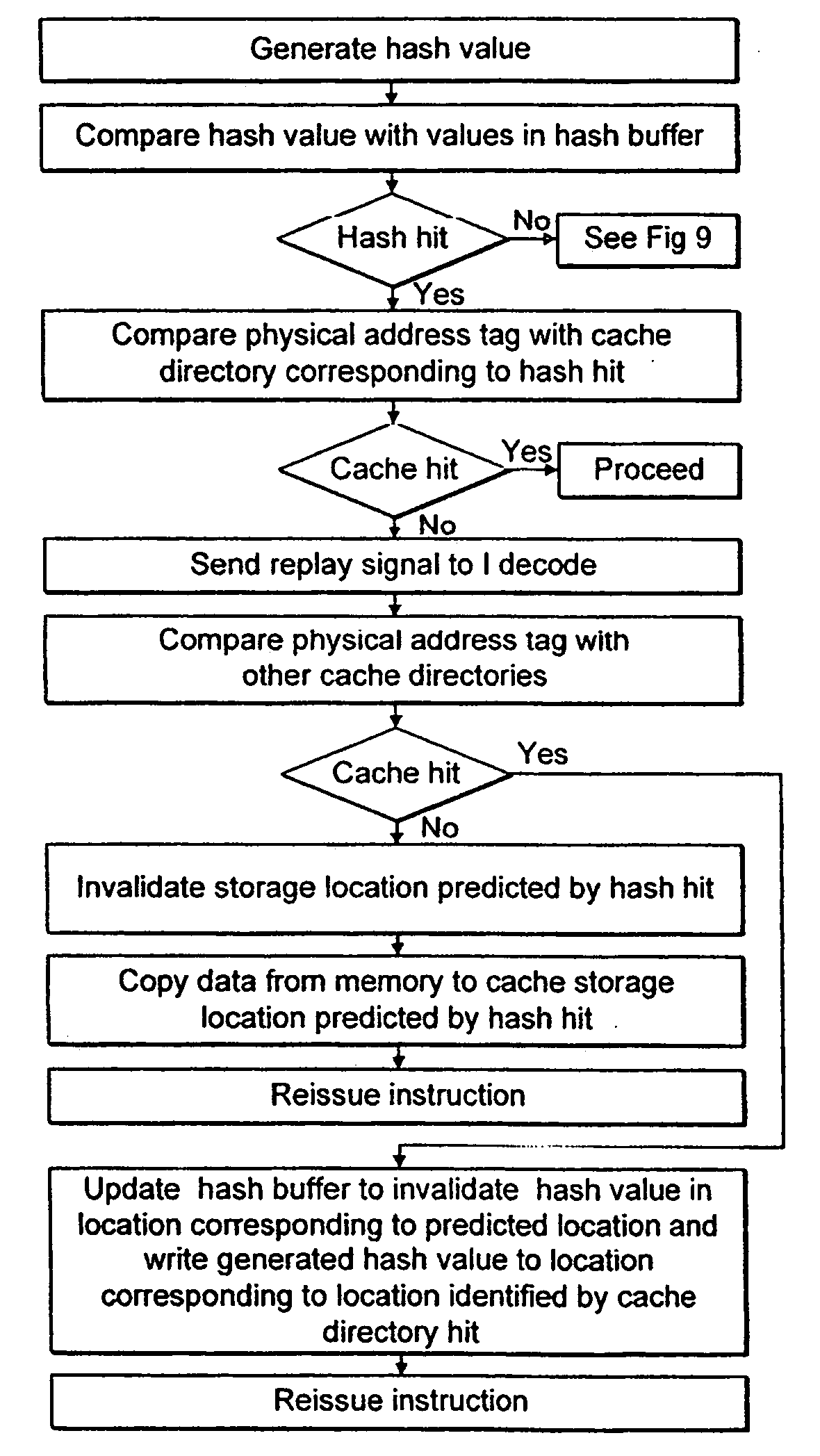

[0051]FIG. 4 shows a way of accessing data in a four way set associative cache 50 within data processor 52 according to an embodiment. A virtual address 81 along with an application or process identifier (ASID / PID) 78 identifying the application or process currently being performed by the data processor is sent to the cache access circuits. The ASID / PID is accessed from a register 75 within the data processor 52 where it is stored. The tag portion of the virtual address 81 along with information from the ASID / PID is then converted to a hash value by hash generator 82. The tag portion of the virtual address in this embodiment is 19 bits wide and it is converted to a 6 bit wide hash value. This value is then compared with the four hash values stored in hash buffer 80 that are indicated as appropriate by the index portion of the virtual address. The hash values that are generated are 6 bit wide, thus this comparison is performed using six bit comparators 64. If a match occurs then this...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com