Pipeline-based circuit with a postponed clock-gating mechanism for reducing power consumption and related driving method thereof

a technology of power consumption and clock-gating mechanism, which is applied in the direction of generating/distributing signals, pulse techniques, instruments, etc., can solve the problems of mainly generated unnecessarily increasing power consumption of logic circuits, and all of the circuit units within logic circuits are not always active, so as to achieve simple circuit structure of second buffer units and achieve successful power saving.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

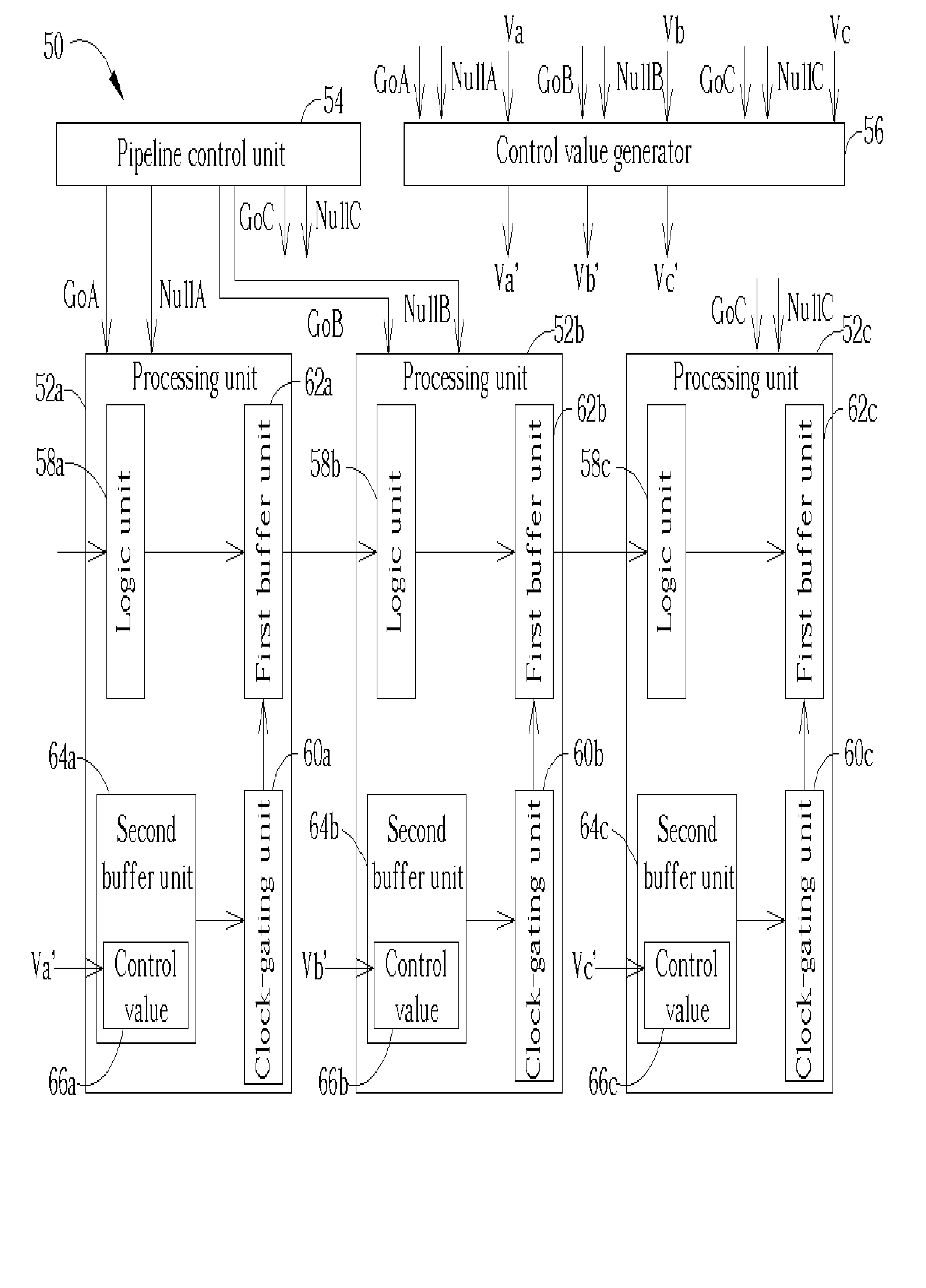

[0024] Please refer to FIG. 6, which is a block diagram of a pipeline-based circuit 50 according to the present invention. The pipeline-based circuit 50, which can be a microprocessor or a digital signal processor (DSP), has a plurality of processing units 52a, 52b, 52c, a pipeline control unit 54, and a control value generator 56. The processing units 52a, 52b, 52c are cascaded to establish a pipeline. Each of the processing units 52a, 52b, 52c has a logic unit 58a, 58b, 58c, a clock-gating unit 60a, 60b, 60c, a first buffer unit 62a, 62b, 62c, and a second buffer unit 64a, 64b, 64c. Taking the processing unit 52a for example, the logic unit 58a is used to perform a predetermined logic operation such as addition or multiplication. The first buffer unit 62a is used to store a calculation result outputted from the logic unit 58a, and to pass the stored calculation result to the next processing unit 52b. The clock-gating unit 60 is used to control a clock signal inputted into the firs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com