Method for producing a multichip module and multichip module

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

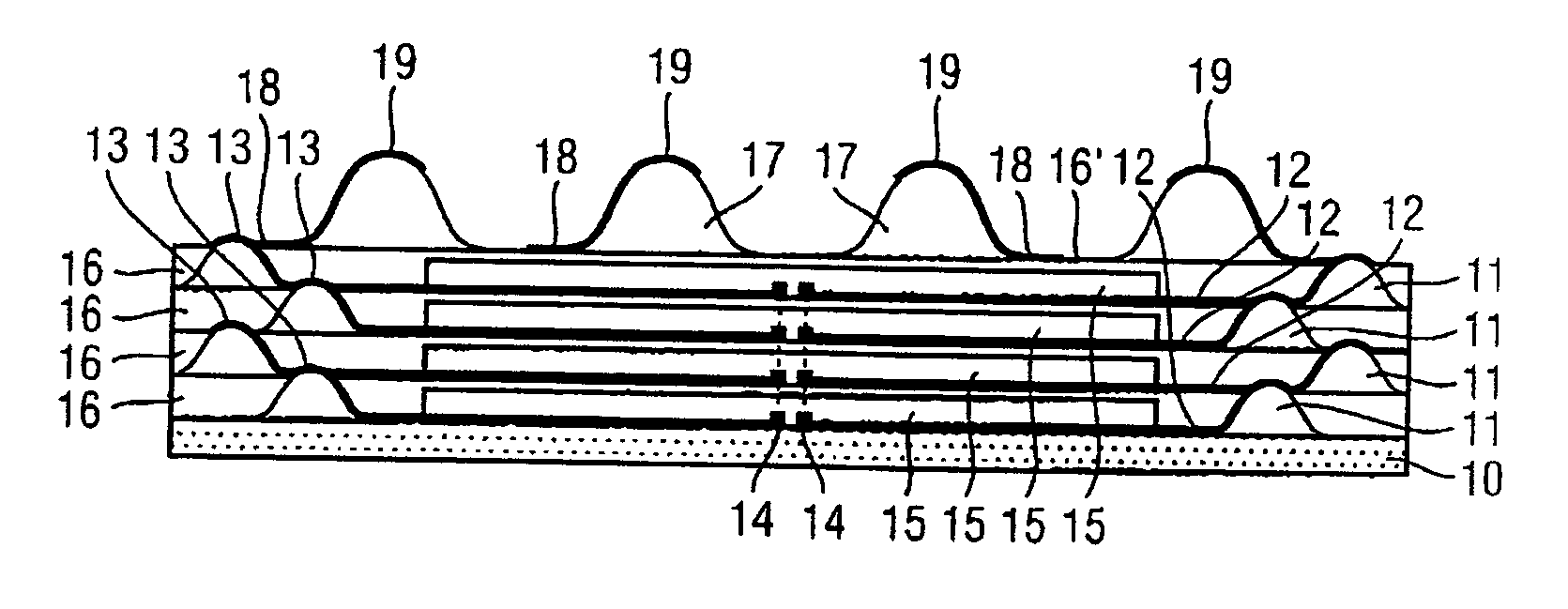

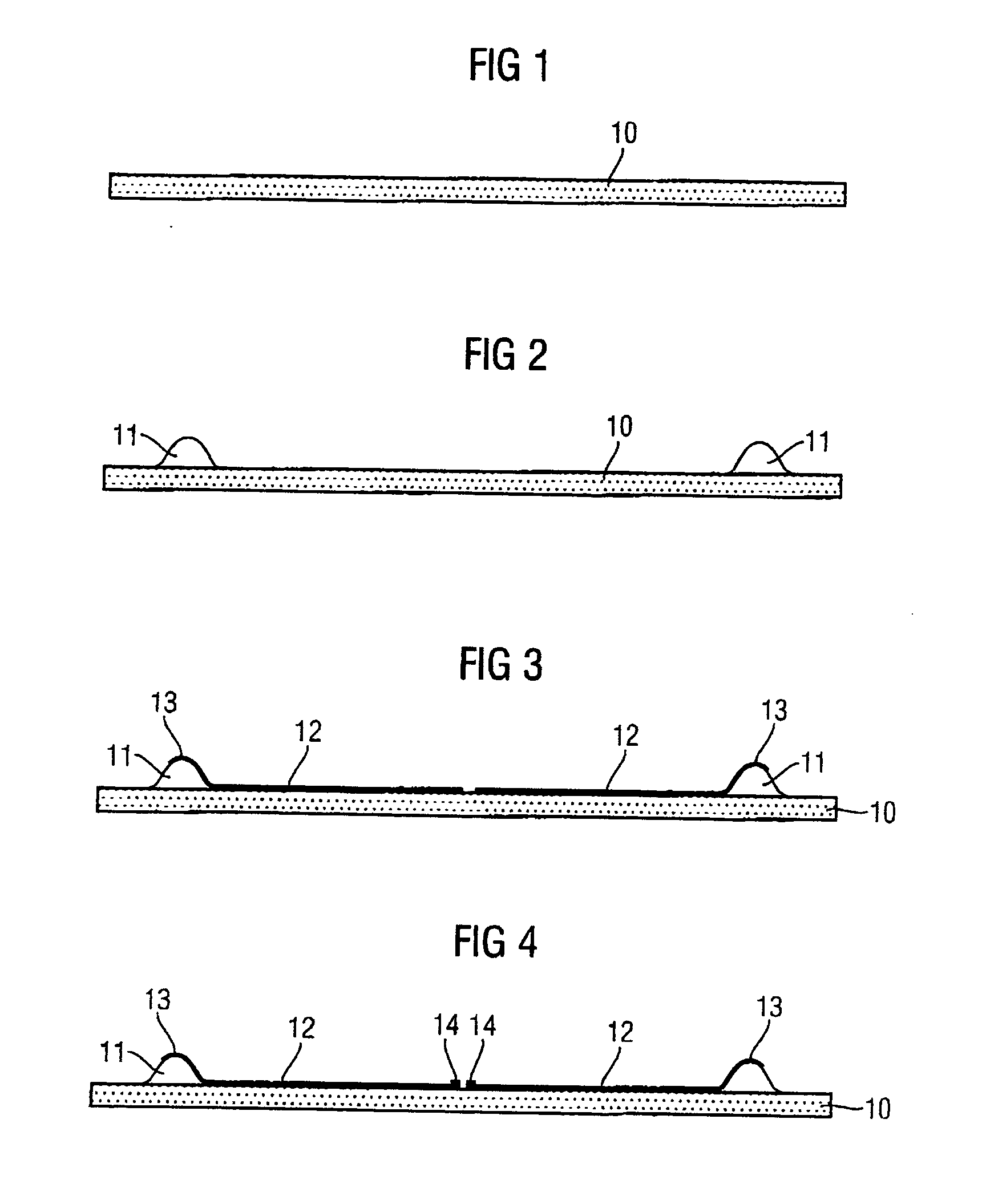

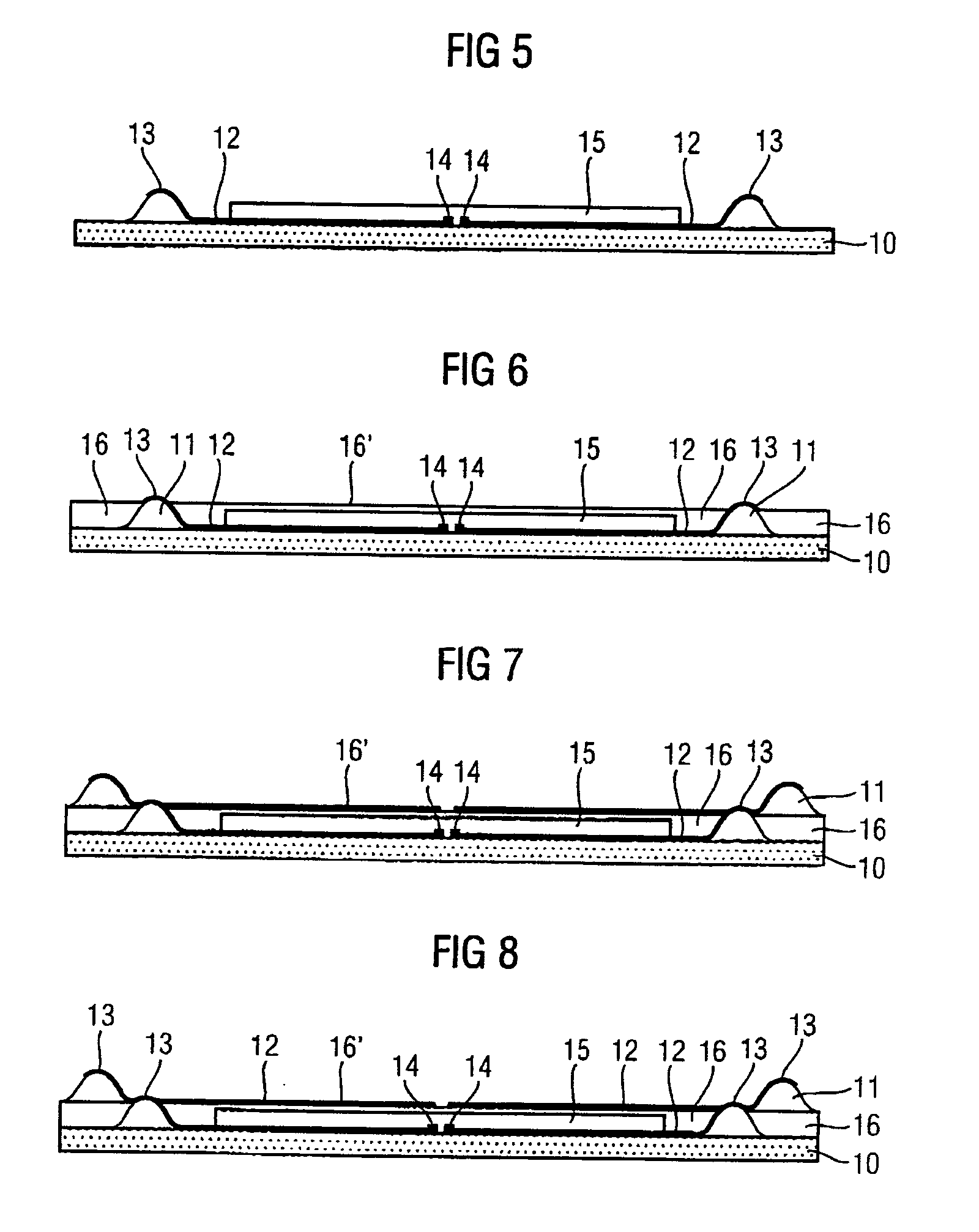

[0038]FIG. 1 illustrates a substrate 10, preferably a sheet, in cross section. In accordance with FIG. 2, at least one contact elevation 11 is applied thereto. The contact elevation 11 is made of a polymer, for example, which may be conductive, such as conductive adhesive, for example, or nonconductive, such as silicone, polyurethane, polyimide, for example. The application of the at least one contact elevation 11 is preferably effected in a printing operation or a metering operation or an injection-molding operation or a stamping step. The at least one contact elevation 11 is preferably bell-shaped and has a small gradient in the transition from the substrate 10 to the contact elevation 11. In this connection, a small gradient is understood to be a gradient of less than 0.5.

[0039] In accordance with FIG. 3, a rewiring device 12 is applied and patterned onto the substrate 10 and the at least one contact elevation 11. In this case, the rewiring device 12 preferably has in each case ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com