Clock distribution networks and conductive lines in semiconductor integrated circuits

a technology of clock distribution network and semiconductor integrated circuit, which is applied in the direction of generating/distributing signals, instruments, basic electric elements, etc., can solve the problems of difficult control of the impedance of lines b>150, the perfect placement of the clock distribution network on the semiconductor die, and the clock propagation speed. the effect of lowering the rc value of lines 150

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The examples in this section are provided for illustration and not to limit the invention. The invention is not limited to particular circuits, materials, processes, process parameters, equipment, or dimensions.

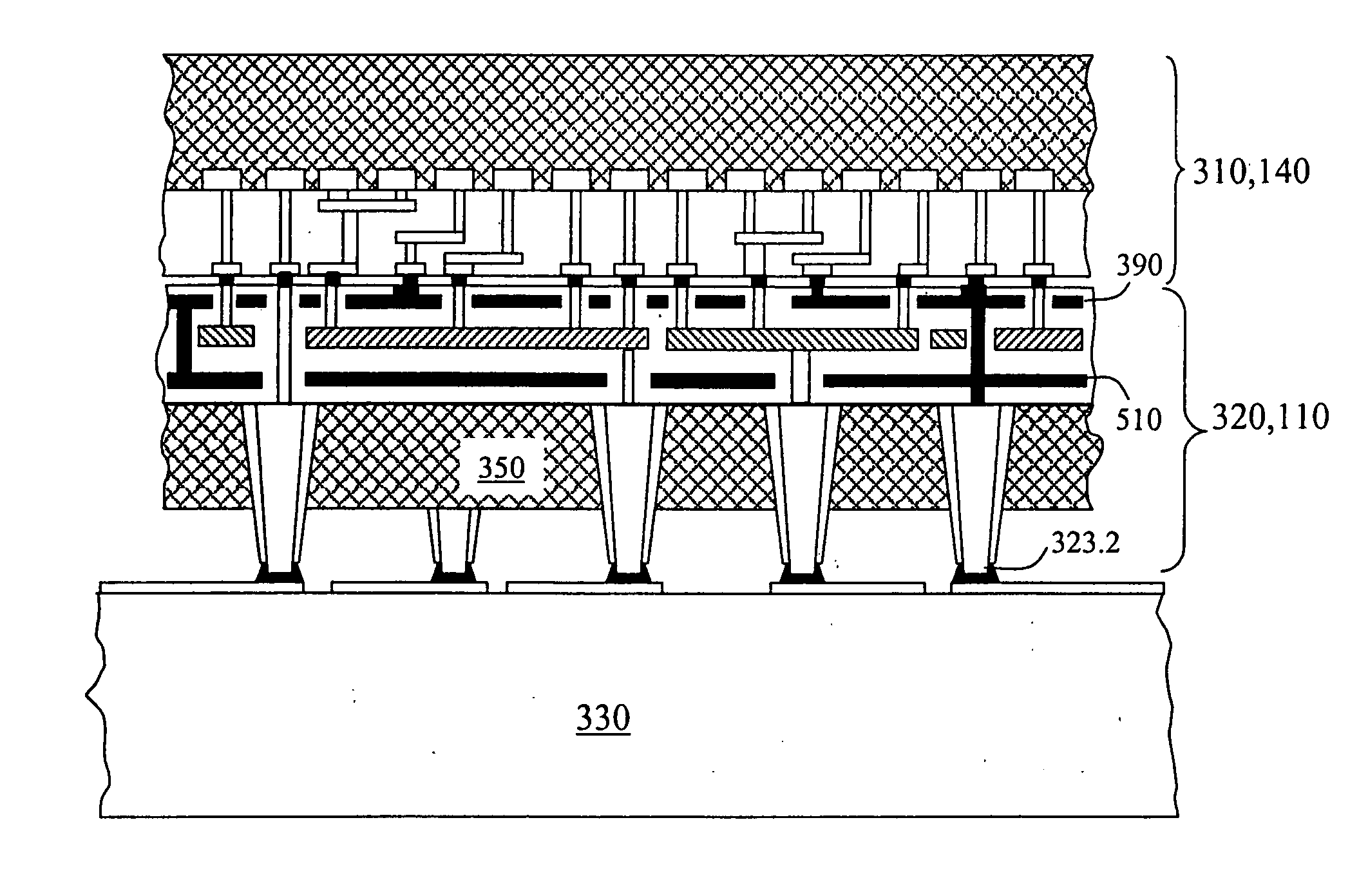

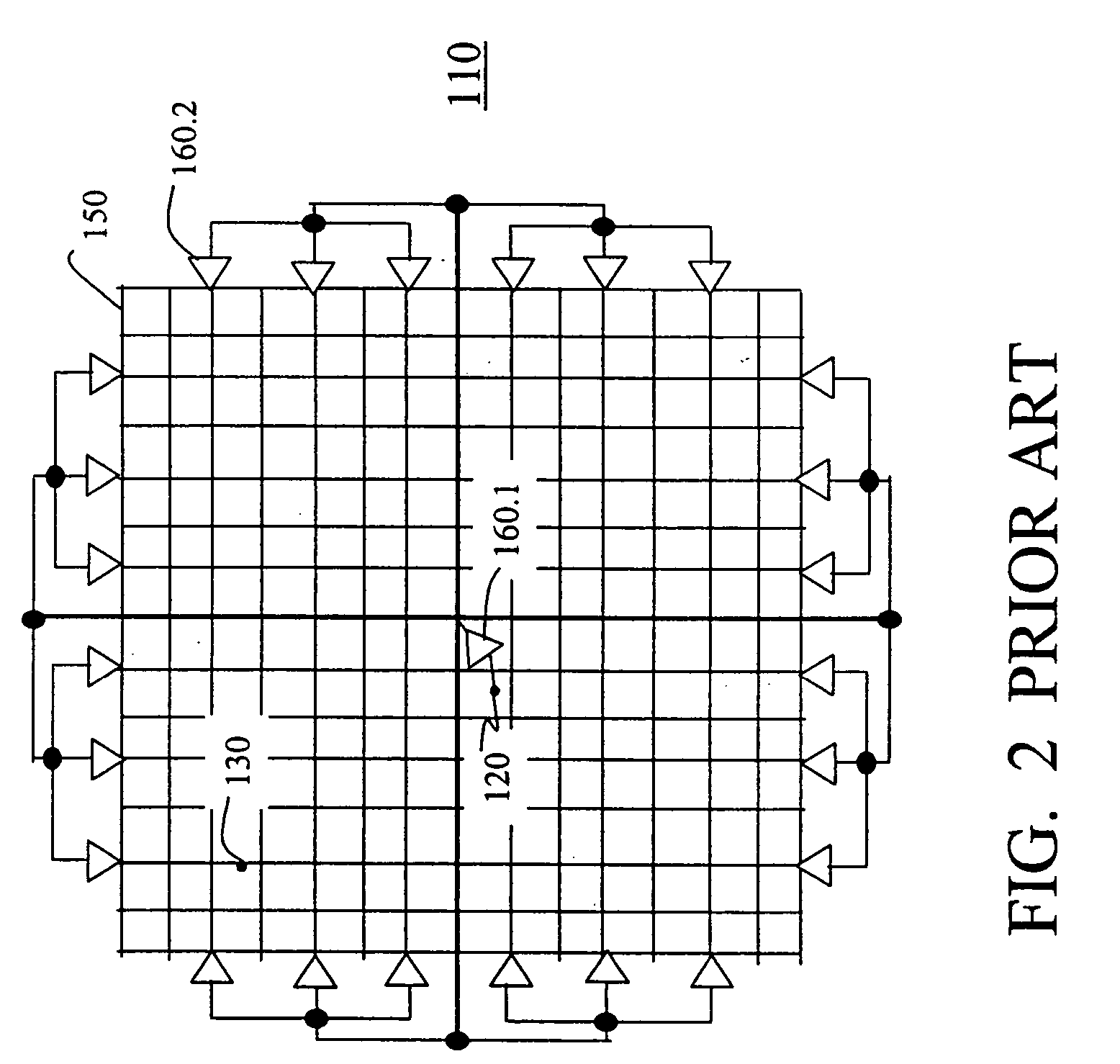

[0031]FIG. 4 illustrates an integrated circuit 310 mounted on another integrated circuit 320 which in turn is mounted on a wiring substrate 330. Each of circuits 310, 320 is a semiconductor die or wafer, or some portion of a semiconductor wafer. Circuit 310 includes clocked circuitry 140 and may also include non-clocked circuitry. For example, circuit 310 may include a microprocessor, a memory, a digital controller, and so on. Circuit 320 is an interposer that contains clock distribution networks 110. The clock distribution networks can be of any type, including the types shown in FIGS. 1, 2, or other types, known or to be invented.

[0032] Circuit 310 includes a semiconductor substrate 340. Active areas 340A may have been formed in substrate 340 for transistors, resis...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com