Floating resistance of I/O circuit on integrated circuit chip

An integrated circuit and resistor technology, which is applied in the field of multiple I/O circuit floating resistors, can solve problems such as increasing product costs, and achieve the effects of improved consistency, good stability, and improved resistance accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

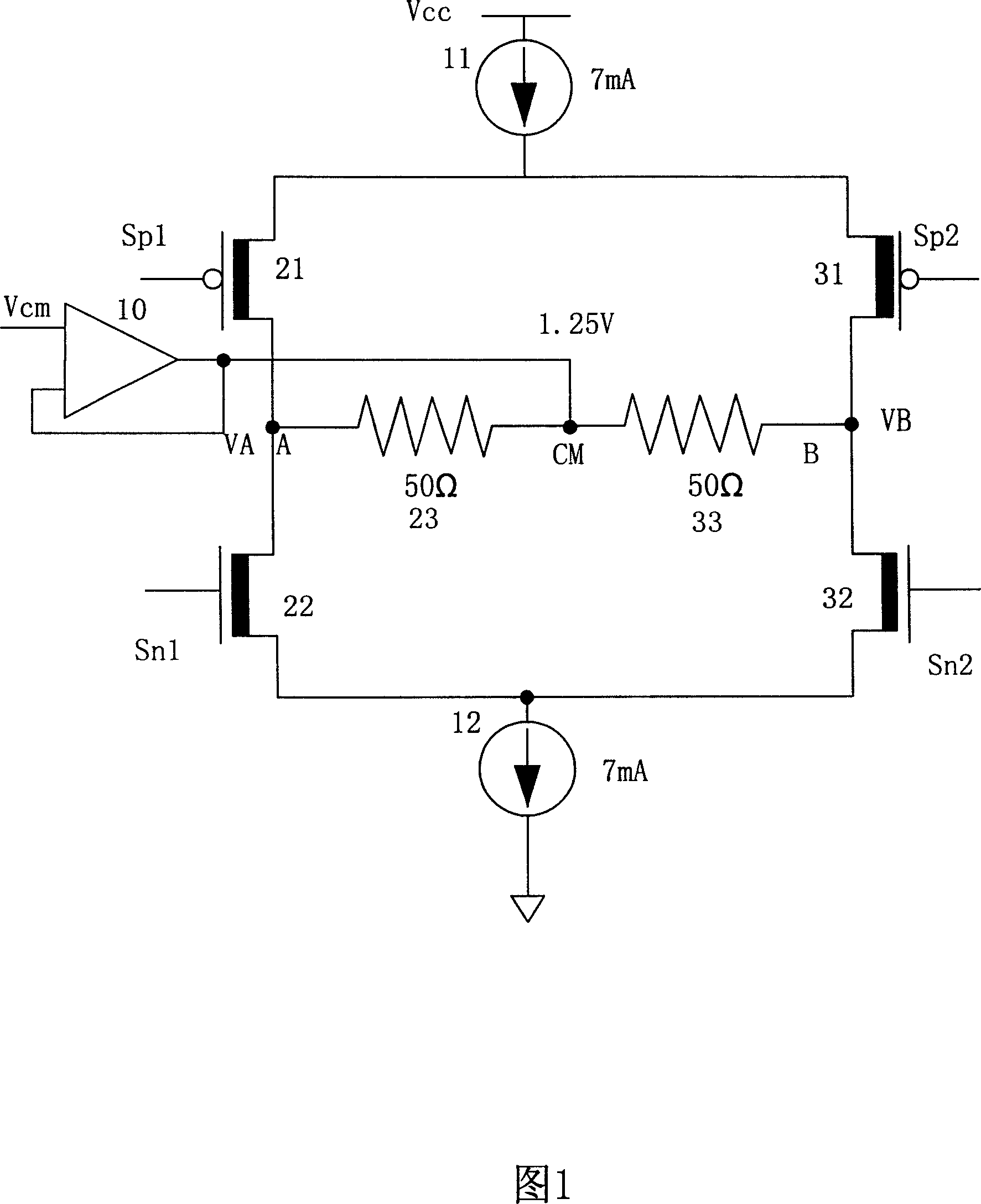

[0017] The electrical structure of a dual low voltage differential signal I / O on a 17-way dual low voltage differential signal (LVDS) I / O integrated circuit chip is shown in FIG. 1 . A P-type field effect transistor 21 and an N-type field effect transistor 22 of the first group of low-voltage differential signal I / O are connected in series between the constant current source 11 connected to the power supply voltage Vcc and the constant current source 12 connected to the ground level , the gate Sp1 of the P-type field effect transistor 21 and the gate Sn1 of the N-type field effect transistor 22 are two input terminals of the first group of low-voltage differential signals. The signal output point A of the first group of low-voltage differential signal I / O, that is, the connection point of the P-type field effect transistor 21 and the N-type field effect transistor 22 is connected with a floating resistor 23 . The other end of the floating resistor 23 is connected to the CM poi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com