Chip electric connection structure and its manufacturing method

A technology of electrical connection and electrical connection pad, which is applied in the field of chip electrical connection structure and its manufacturing method, can solve the problems of poor electrical performance and reliability of the manufacturing process, simplify the manufacturing process and interface integration, and avoid electrical conduction and Molding, ensuring electrical performance and the effect of

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

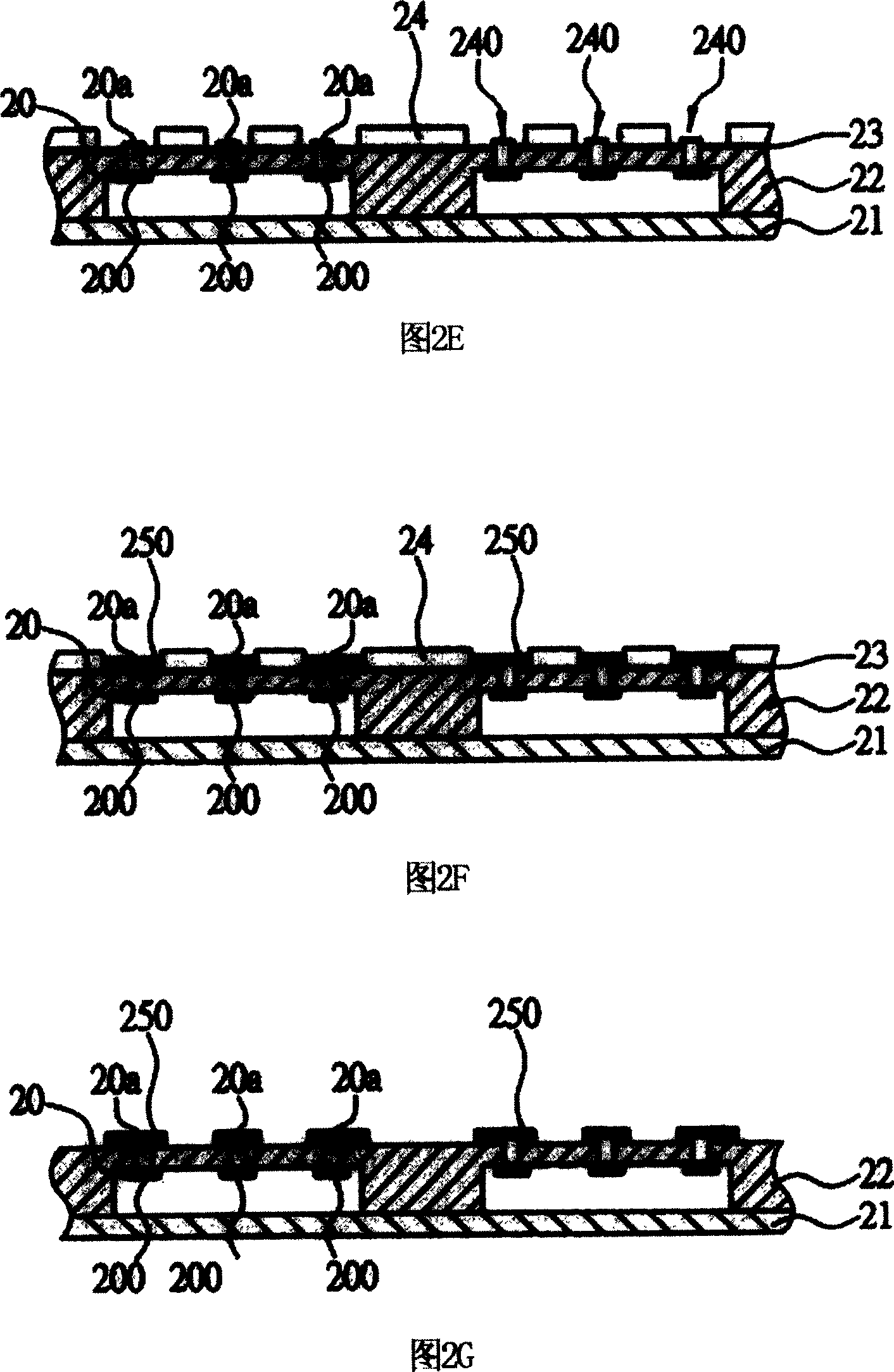

[0024] 2A to 2G are schematic cross-sectional views of the manufacturing method of the chip electrical connection structure of the present invention.

[0025] As shown in FIG. 2A , firstly, at least one semiconductor chip 20 is provided, and conductive bumps 20 a are formed on the electrode pads 200 of the semiconductor chip 20 . The conductive bump 20a may be formed by any one of the conductive metal group consisting of copper, gold, silver, tin, nickel and palladium or formed by laminating multiple layers of the above metals. According to practical experience, the metal bump is preferably made of copper, but not limited thereto. In addition, the conductive bump can be formed by means of electroplating, physical deposition or chemical deposition. Since the manufacturing method is not the main technical feature of the present invention, it will not be repeated here.

[0026] As shown in FIG. 2B , at least one semiconductor chip 20 is mounted on a carrier 21 . The semiconduct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com