Insulated gate field effect transistor and manufacturing method thereof

A field effect transistor, insulated gate type technology, which is applied to the insulated gate type field effect transistor and its manufacturing field to realize the reduction of feedback capacitance, can solve the problems of limited high-frequency switching characteristics, etc., to reduce on-resistance and improve high-frequency characteristics, the effect of reducing the number of masks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

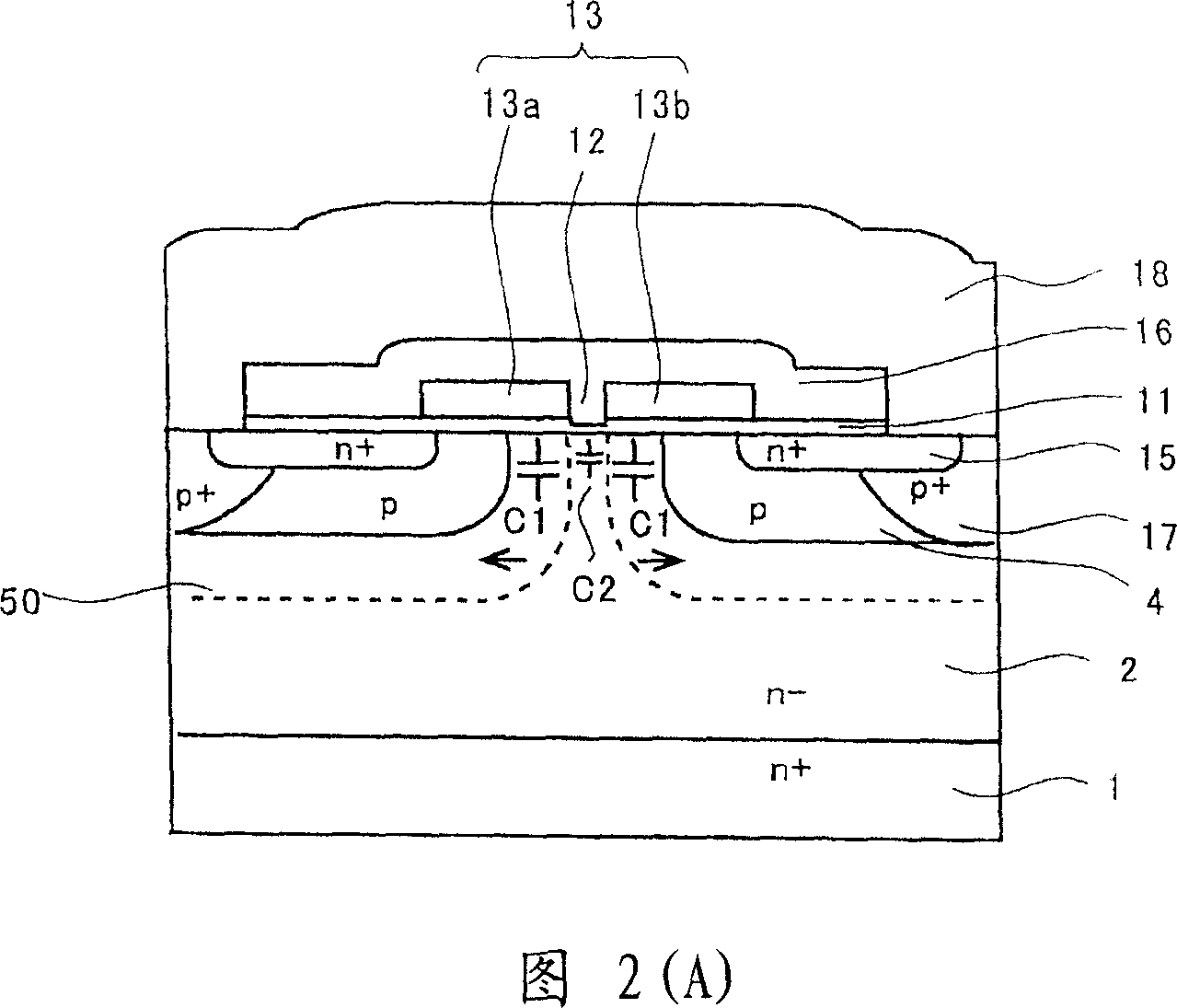

[0069] Referring to FIGS. 1 to 15 , an embodiment of the present invention will be described by taking an n-channel MOSFET as an example.

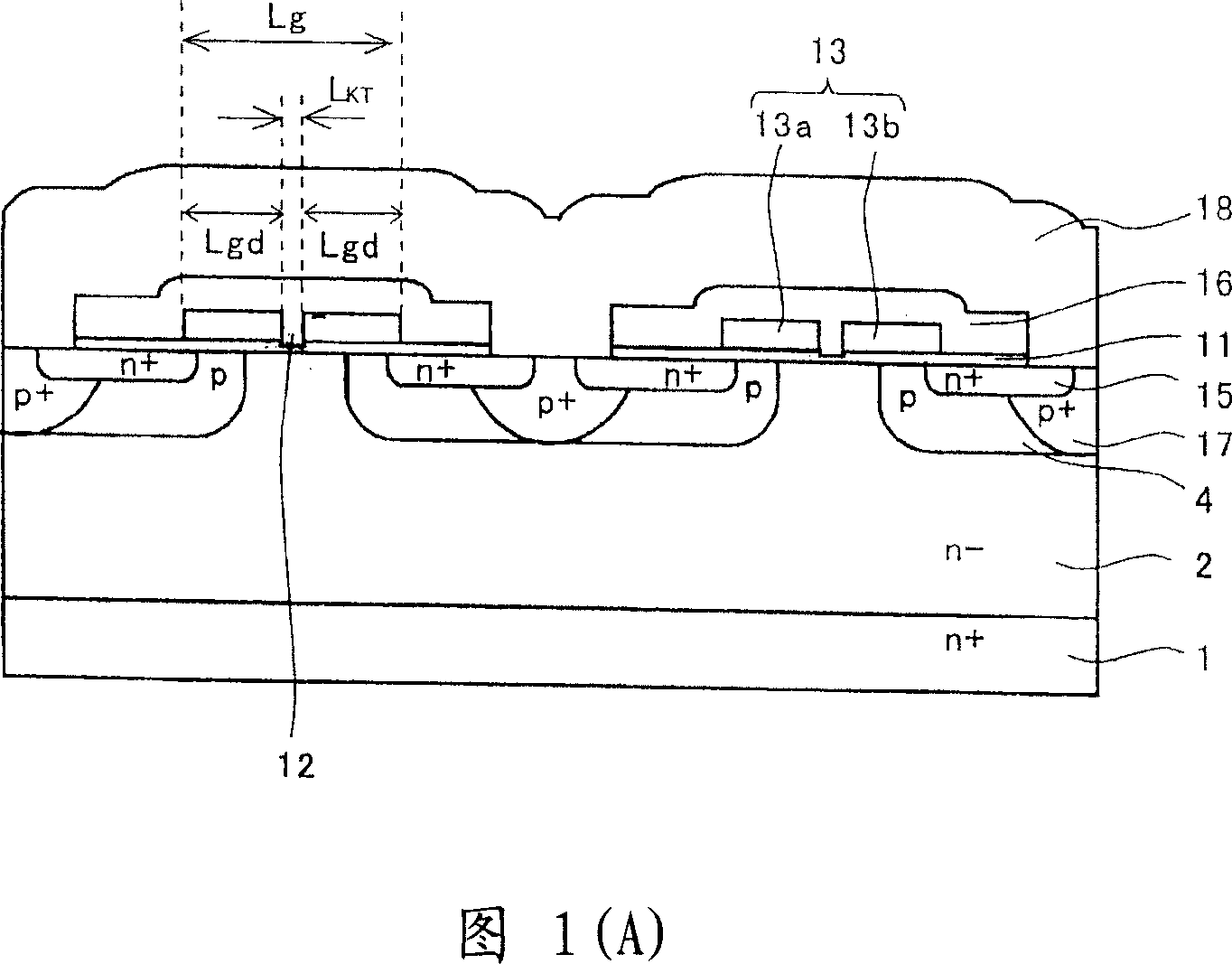

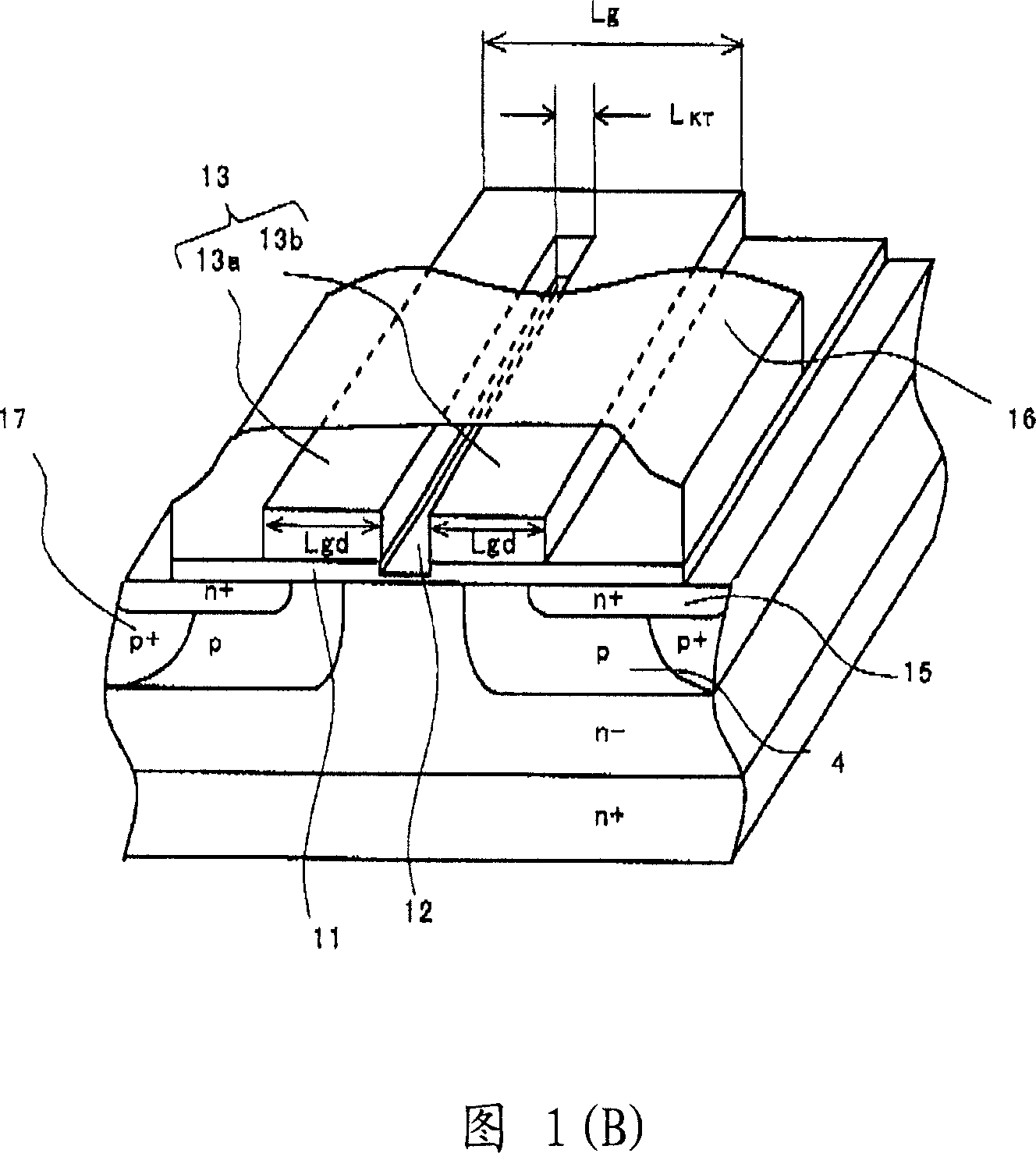

[0070] FIG. 1 is a diagram showing the structure of a MOSFET of the present embodiment of the first embodiment. FIG. 1(A) is a sectional view, and FIG. 1(B) is a perspective view.

[0071] The MOSFET has a semiconductor substrate 1 , a semiconductor layer 2 , a channel region 4 , a gate electrode 13 , a separation hole 12 , a gate insulating film 11 , an interlayer insulating film 16 , a source region 15 , and a body region 17 .

[0072] For example, an n-type epitaxial layer 2 is stacked on an n+ type silicon semiconductor substrate 1 to provide a drain region. A p-type channel region 4 is provided on the surface of the n-type epitaxial layer 2 . A plurality of channel regions 4 are provided on the surface of the epitaxial layer 2 by ion implantation and diffusion. In addition, there are cases where a low-resistance layer is formed on ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com