Silicon-on-nothing metal-oxide-semiconductor field-effect-transistor and method for manufacturing the same

A technology of oxide semiconductors and field effect transistors, which is applied in the field of metal oxide semiconductor field effect transistors and its manufacturing, and can solve problems such as complex methods

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The present invention will now be described in conjunction with preferred embodiments with reference to the accompanying drawings.

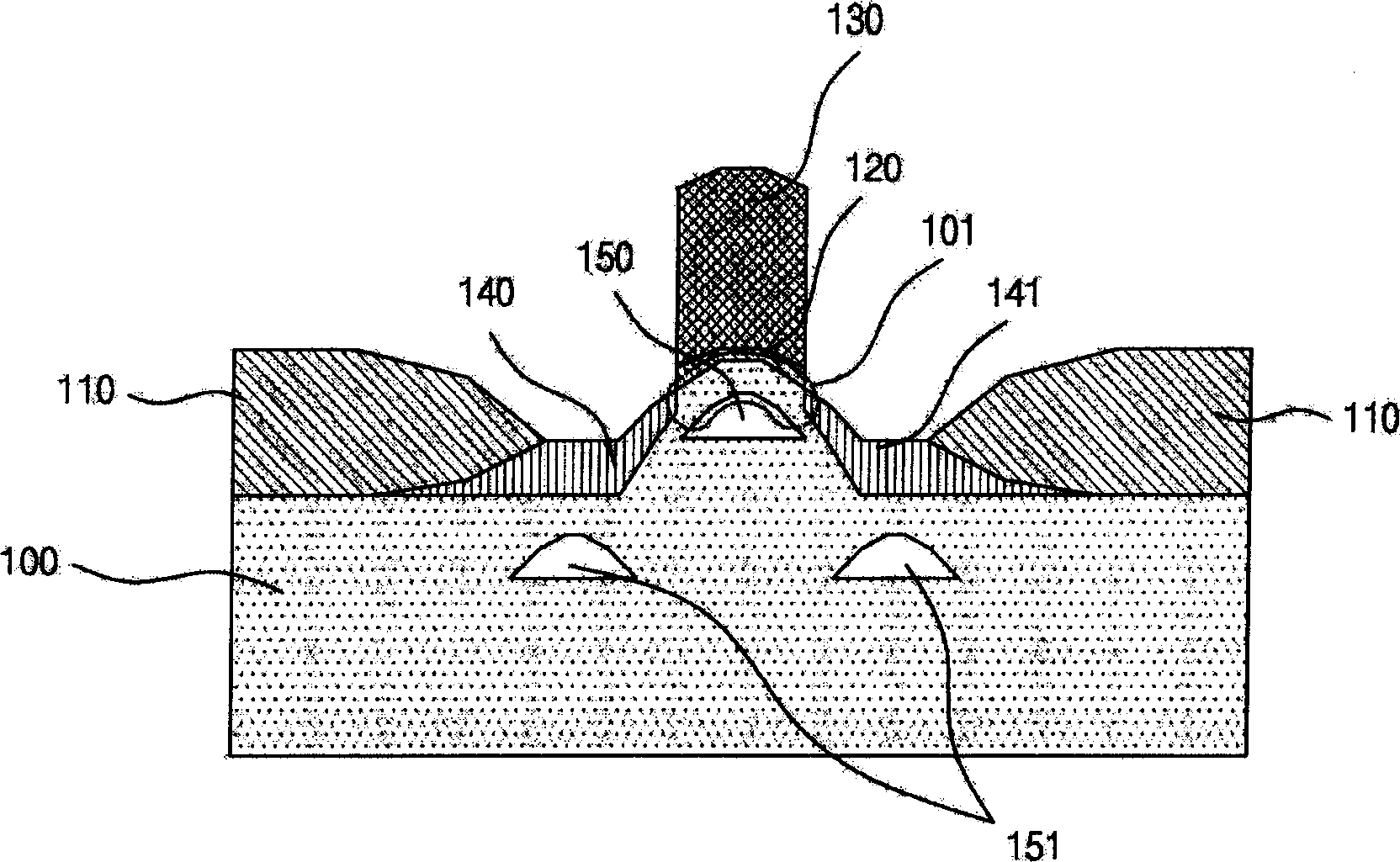

[0046] Refer to the following figure 2 A SON MOSFET according to one embodiment of the present invention is described. figure 2 is a cross-sectional view of a SON MOSFET according to one embodiment of the present invention.

[0047] refer to figure 2 , The SON MOSFET according to one embodiment of the present invention includes a silicon substrate 100, an isolation insulating film 110, a gate insulating film 120, a gate 130, a source region 140, a drain region 141, bubbles 150, 151 and a silicon channel 101.

[0048] Isolation insulating films 110 are formed on both sides of the top of the silicon substrate 100 . A gate insulating film 120 and a gate electrode 130 are sequentially stacked on the surface of the silicon substrate 100 between the isolation insulating films 110 . The isolation insulating film 110 is used to electrically...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com