Multiplier based on improved Montgomey's algorithm

A modular multiplier and algorithm technology, applied in the field of modular multipliers based on the improved Montgomery algorithm, can solve the problems of many calculation cycles, large VLSI implementation area, large critical path delay, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

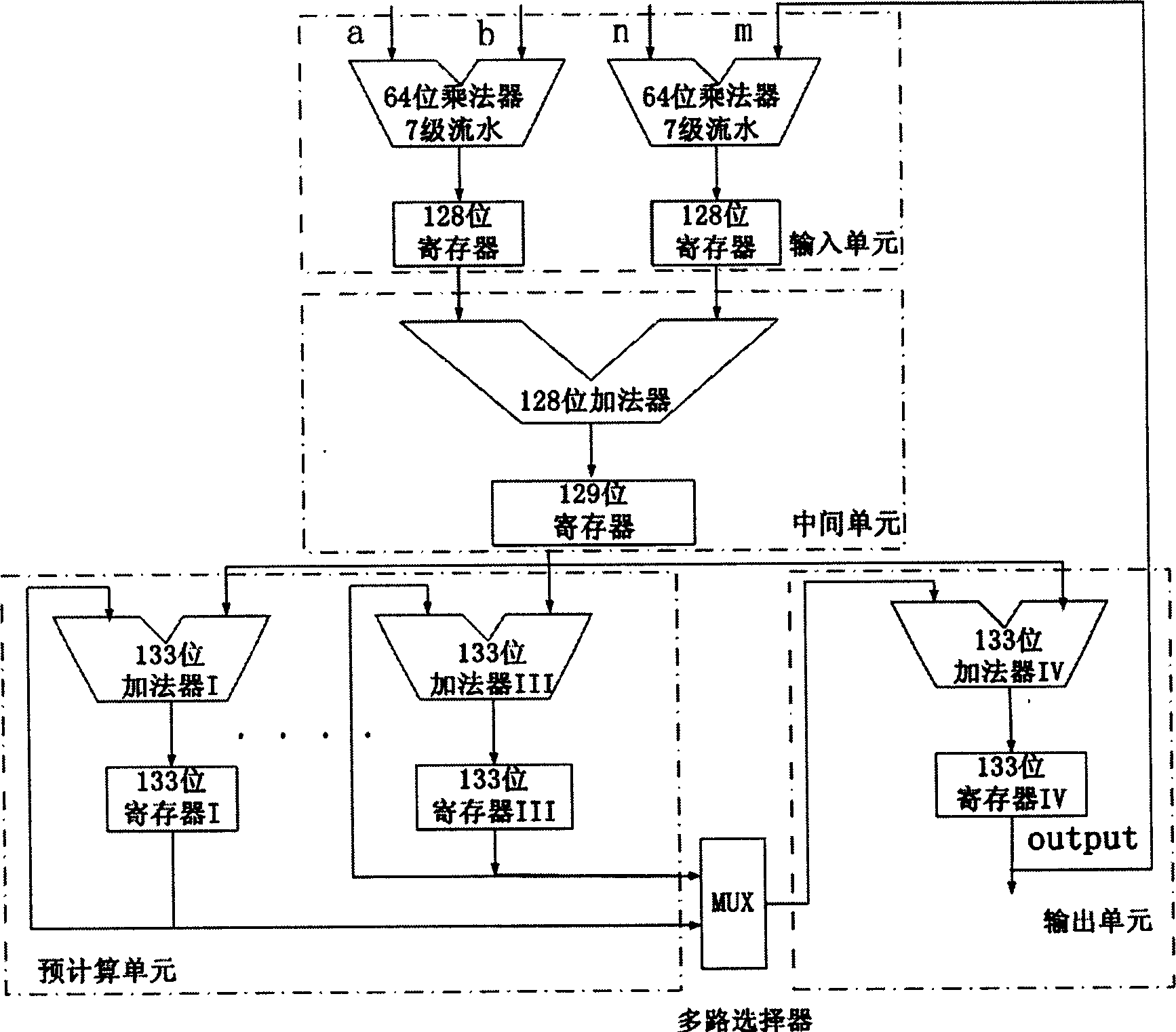

[0066] The modulus multiplier circuit structure of this design is as follows: figure 1 As shown, it is implemented with an ASIC chip.

[0067] The entire data path is composed of five units: input unit, intermediate unit, pre-calculation unit, output unit and multiplexer. The input unit includes three input ports a, b, n and two 64-bit multipliers; the intermediate unit includes a 128-bit adder and a 129-bit register; the pre-calculation unit consists of adder I, adder II, adder III And register I, register II, register III; the output unit is composed of adder IV and register IV.

[0068] A feature of this design is that although the operands of the modular multiplier have been decomposed into 64-digit numbers with a relatively short bit length, the delay of the 64-bit multiplier is still relatively large, and it still reaches More than 20ns, which limits the clock frequency of the system. Therefore, this design uses a multiplier with 7-stage pipeline structure to shorten ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com