Method for generating gate controlled clock unit according to standard cell base element directly

A standard cell library, gated clock technology, applied in instruments, electrical digital data processing, special data processing applications, etc., can solve the problems of gated clock cell instantiation, high cost, loose device connection, etc., to achieve low power consumption Design, easy to generate, easy to use effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

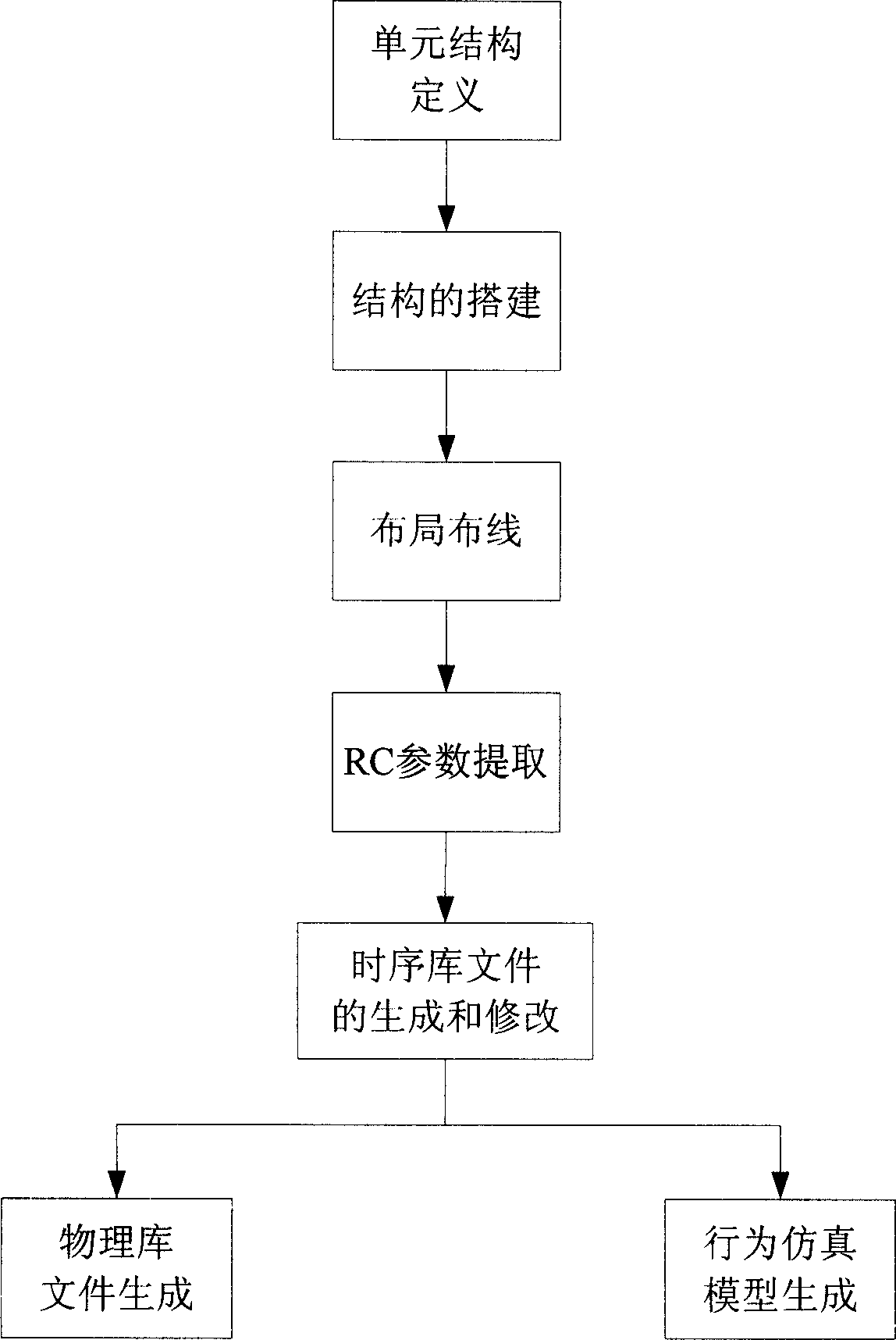

[0041] Such as figure 1 As shown, the present invention will be further described below in conjunction with the examples, but the present invention is not limited to these examples.

[0042] It is necessary to design a latch-based back-end control rising edge gated clock unit (latch_posedge_postcontrol). The specific steps to be performed are:

[0043] 1. Determine the gated clock unit structure using latch_posedge_postcontrol, and determine the relevant pin functions;

[0044] clock_gate_enable_pin: module clock enable signal module_clk_en;

[0045] clock_gate_clock_pin: input clock signal clkin;

[0046] clock_gate_test_pin: test mode enable signal test_clk_en;

[0047] clock_gate_out_pin: output clock signal clkout;

[0048] 2. Construction of the structure:

[0049] According to the selected clock_gating_cell structure, directly use the gate-level structure to write the rtl code (code omitted). The code forms a clock_gating_cell of latch_poedge_precontrol. For this ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com