Semiconductor device and method for fabricating the same

一种制造方法、半导体的技术,应用在半导体/固态器件制造、半导体器件、电气元件等方向,能够解决控制范围缩小等问题,达到提高穿通耐压、扩大控制范围的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

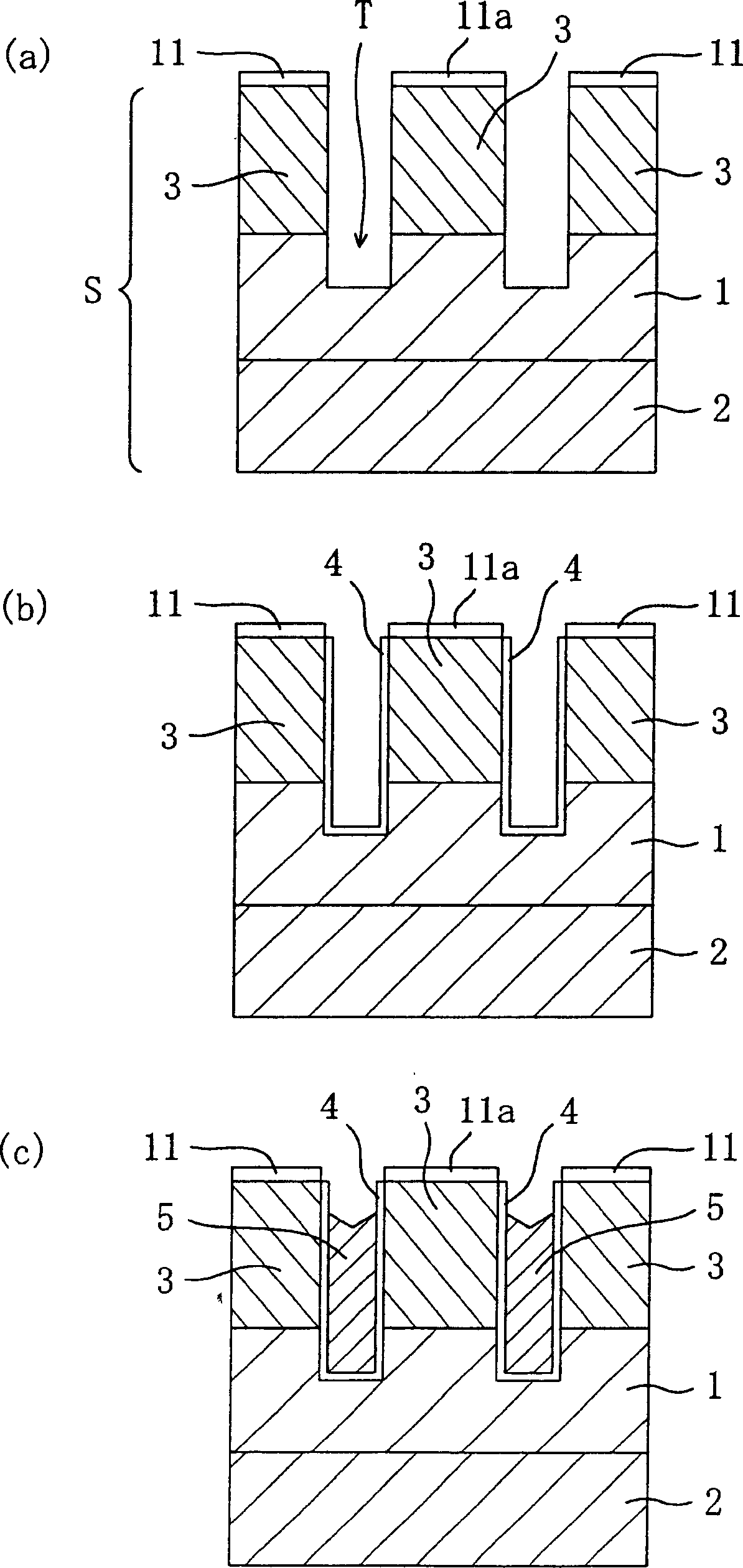

[0030] —Manufacturing of semiconductor devices—

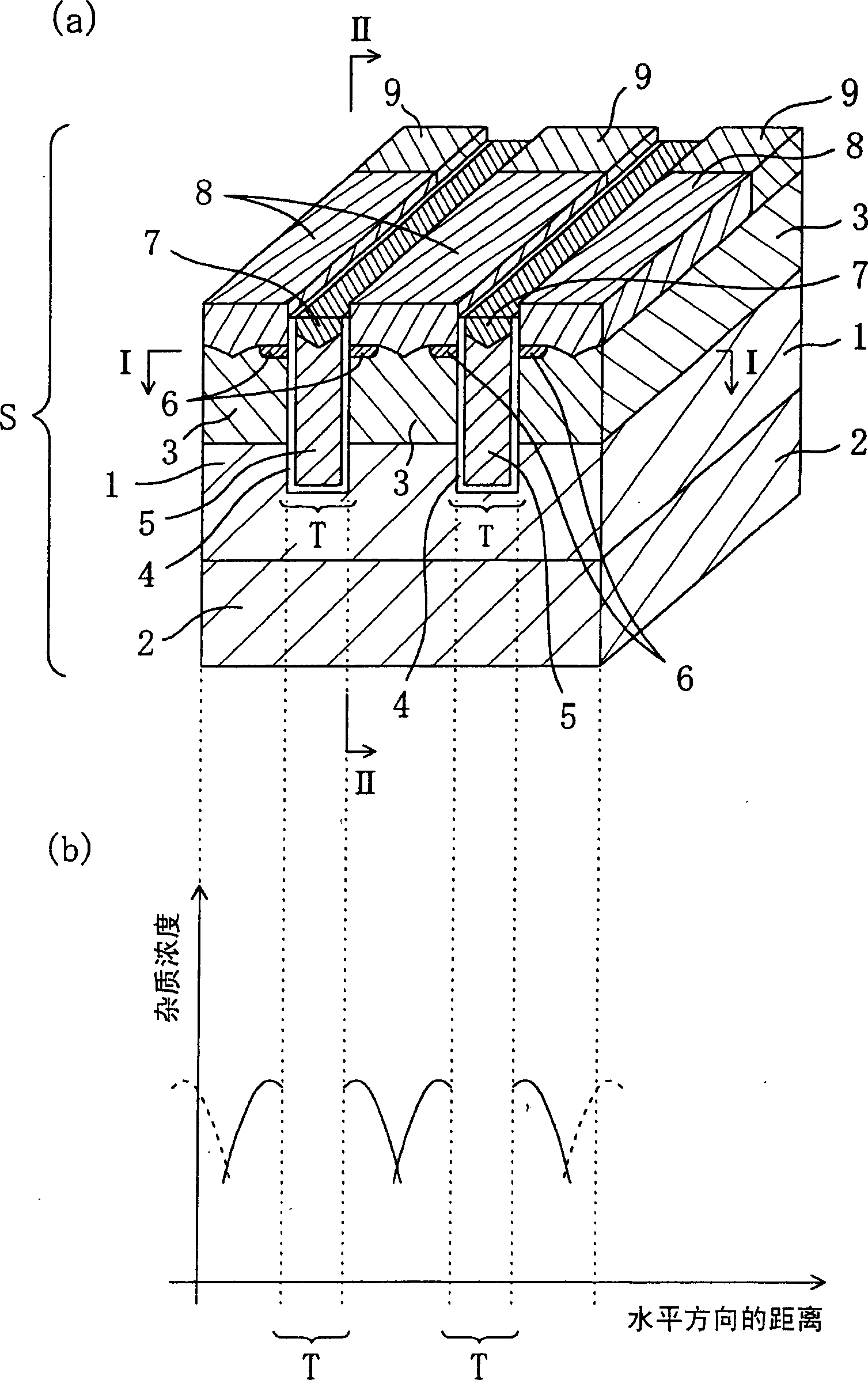

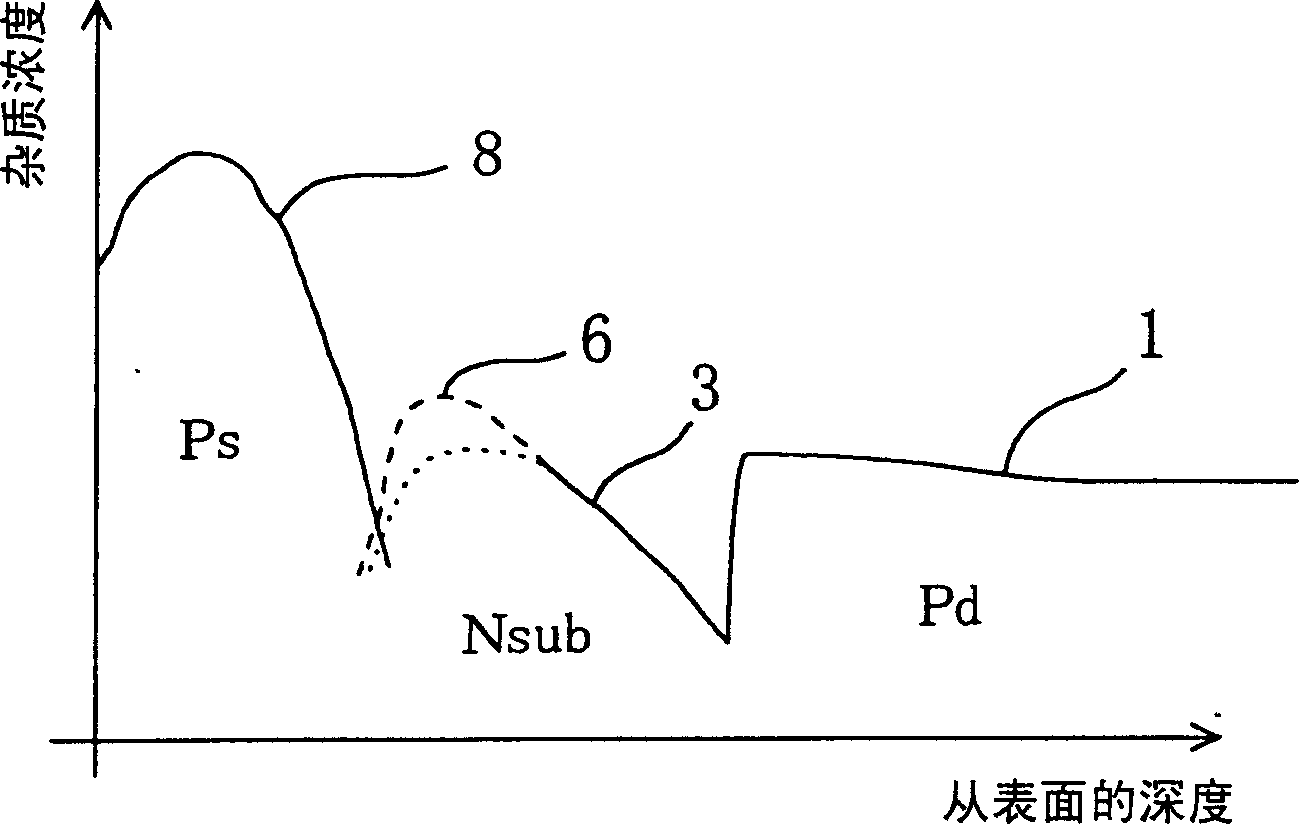

[0031] figure 1 (a) and (b) are perspective views showing the structure of the semiconductor device having the trench gate structure in Embodiment 1, and diagrams showing impurity concentration distribution along a cross-section shown by line I-I. In addition, in figure 1 In (a), the pairs of Figure 4 (c) A representation of the silicide layer 10 shown.

[0032] Such as figure 1 As shown in (a), the semiconductor device of this embodiment includes: a high-concentration P-type drain region 2 formed on a silicon substrate S, and a low-concentration P-type drain region (EPI) 1 provided on the high-concentration P-type drain region 2 , a high-concentration P-type source region 8 formed above the low-concentration drain region 1 , and an N-type substrate region 3 formed between the high-concentration P-type source region 8 and the low-concentration P-type drain region (EPI) 1 . In addition, a trench T for forming a gate ele...

Embodiment approach 2

[0052] —Structure of semiconductor device—

[0053] Figure 6 (a) and (b) are perspective views showing the structure of a semiconductor device having a trench gate structure according to Embodiment 2 of the present invention, and diagrams showing impurity concentration distribution along a cross section indicated by line VI-VI. In addition, in Figure 6 In (a), for the sake of easy to see the structure, the pair Figure 5 (c) A representation of the silicide layer 10 shown. The structure of the semiconductor device of this embodiment is basically the same as that of Embodiment 1 (see figure 1 (a)) are the same, and therefore descriptions of parts having the same structure are omitted.

[0054] Such as Figure 6 As shown in (a), in the semiconductor device of this embodiment, the N-type pocket region 6B is formed in the entire region between the N-type substrate region 3 and the high-concentration P-type source region 8 . That is, in the semiconductor device of the pres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com