Method for mfg. electrostatic discharge protector by deep amicron process

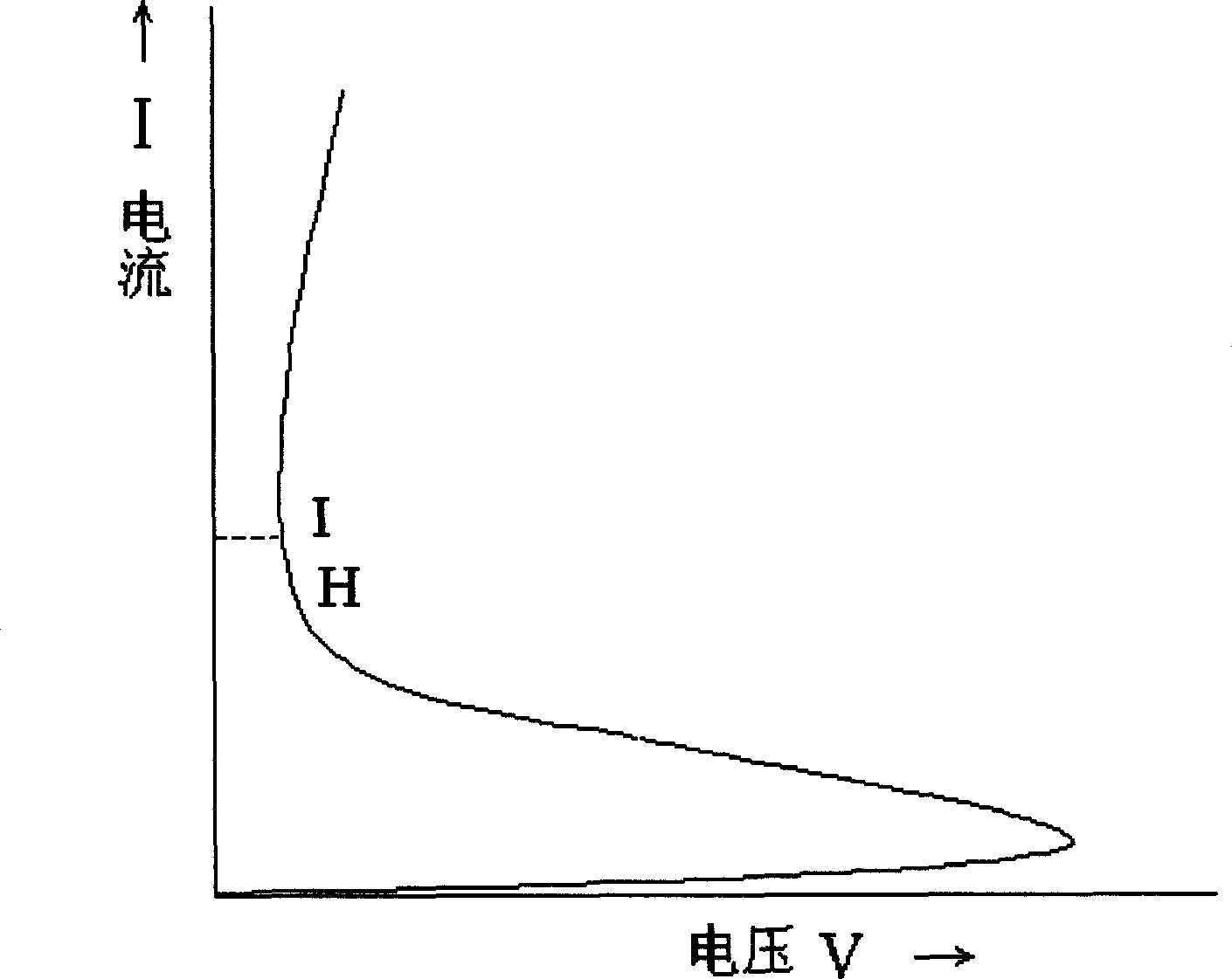

A technology of electrostatic discharge protection and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problems of no resistance buffer, no resistance buffer, ESD protection structure damage, etc., to avoid damage Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] The invention is used to improve the shortcomings of electrostatic discharge (ESD) protection components in the self-aligned metal silicide process, and adopts the method of self-aligned metal silicide barrier (salicide block) to make the polysilicon gate in the ESD protection component area There is no metal silicide formation on the electrode and source / drain regions, so that there is a resistance ballast between the drain contact (drain contract) and the polysilicon gate (poly gate), which can allow the high current generated by electrostatic discharge It can be removed in a more uniform way, so local high current and local heating will not occur near the drain.

[0028] Figure 5 to Figure 9 They are cross-sectional views of each step of making internal circuits and transistors of the electrostatic discharge protection device in a preferred embodiment of the present invention, taking N-type transistors (NMOS) as an example to describe the manufacturing process of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com