Technique for repairing salient point and memory by using laser

A laser repair and memory technology, which is applied in the fields of electrical solid-state devices, semiconductor devices, and semiconductor/solid-state device manufacturing, etc., can solve problems such as weakening, detection mark oxidation, metal layer 24 adhesion, and diffusion barriers.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

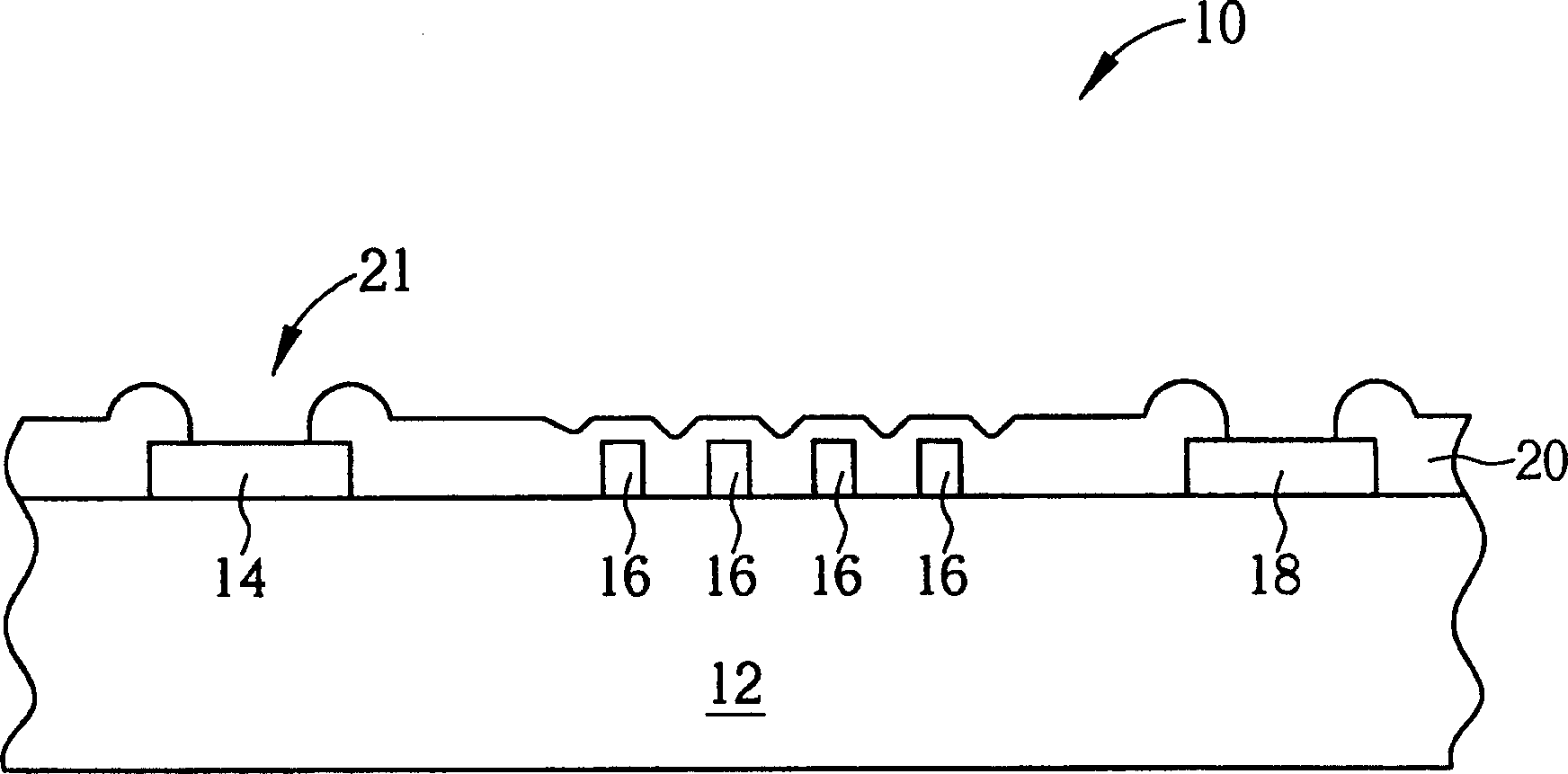

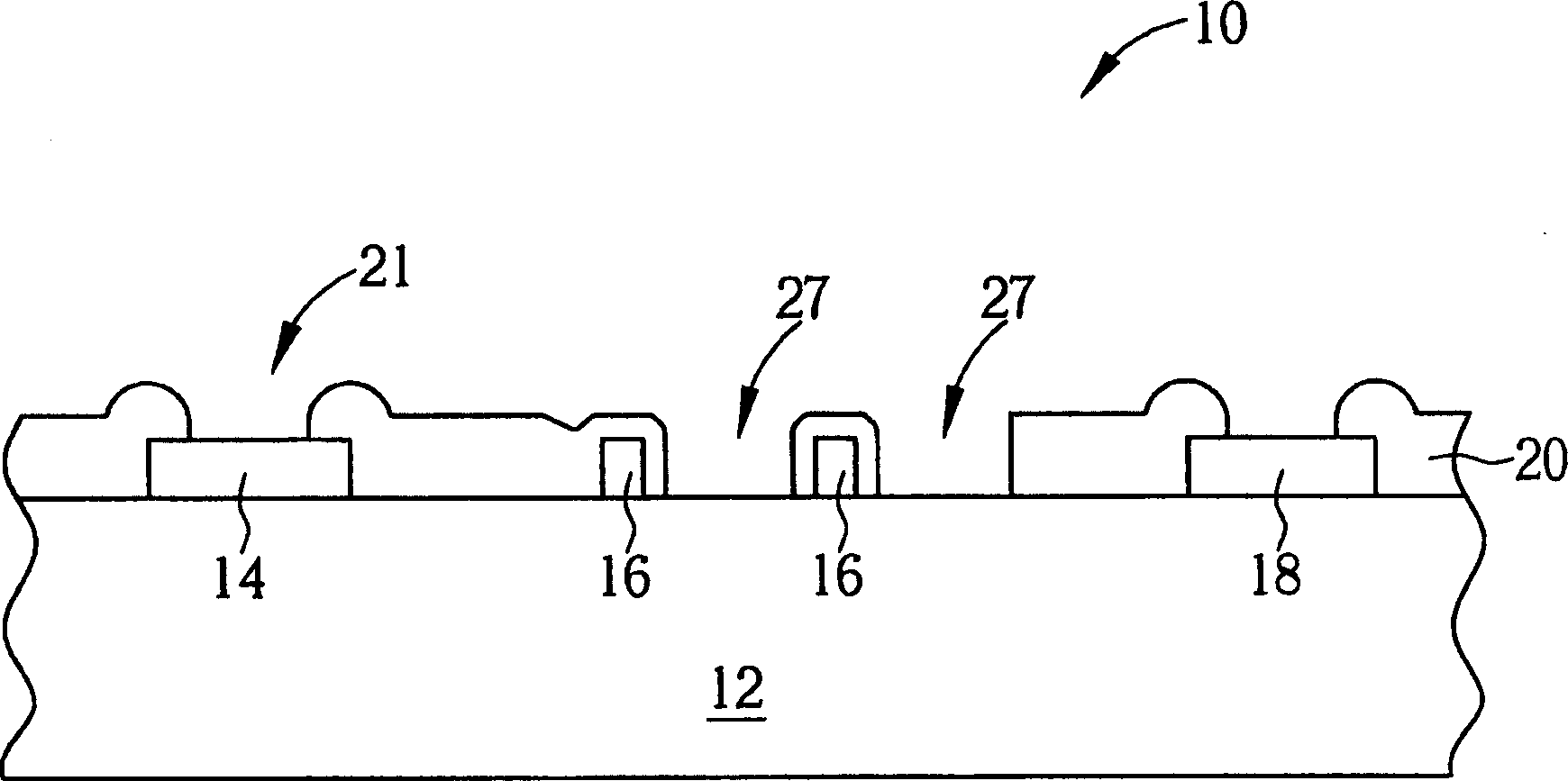

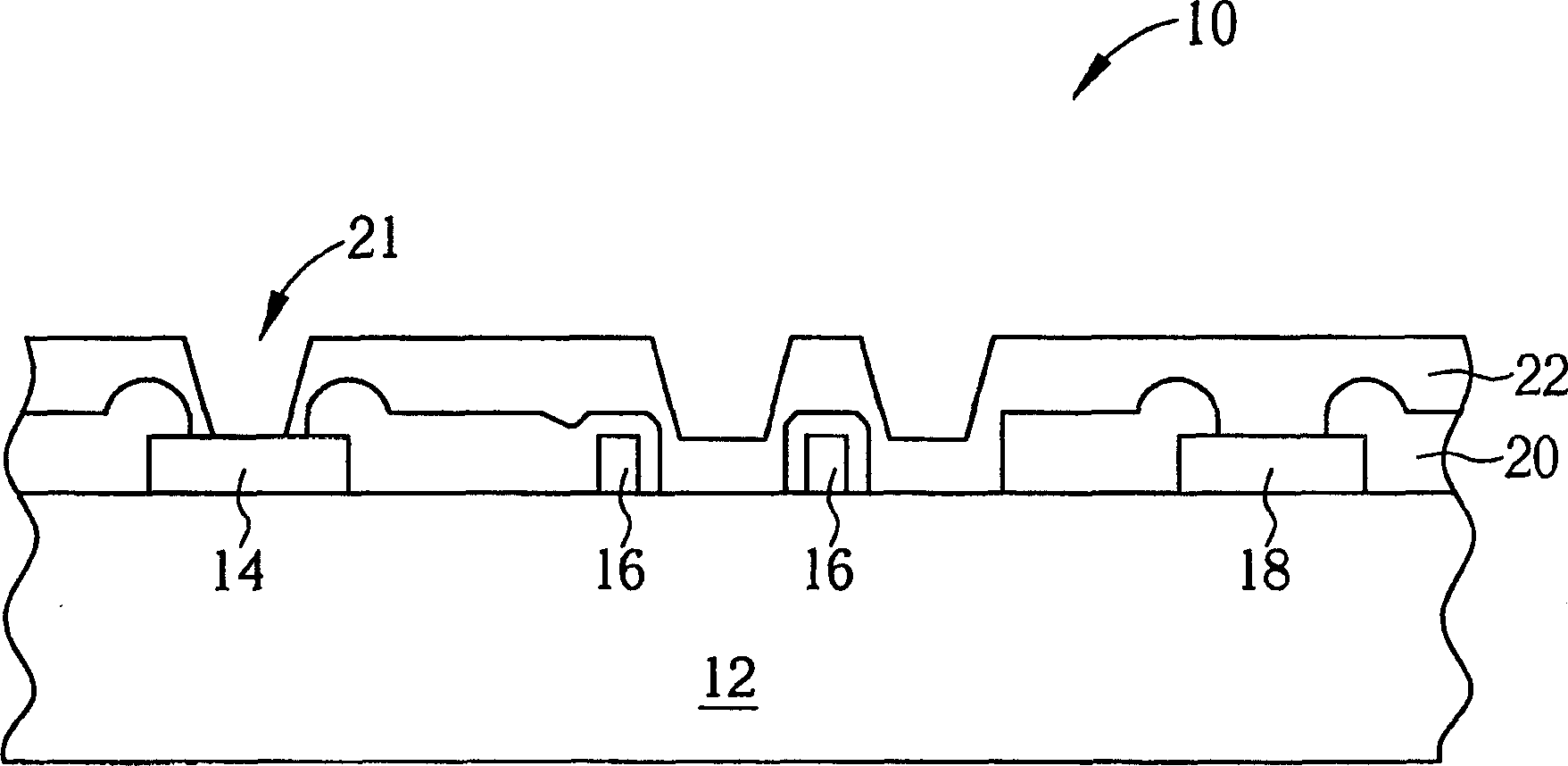

[0024] Please refer to Figure 5 to Figure 7 , Figure 5 to Figure 7 It is a schematic diagram of a first embodiment of performing a bump and memory laser repair process on a semiconductor chip 40 according to the present invention. Such as Figure 5 As shown, the semiconductor chip 40 includes a substrate 42 on which an integrated circuit region (not shown) is formed, and the integrated circuit region includes an embedded memory array. Wherein, the substrate 42 additionally includes a bump pad 44, a plurality of fuse structures 46 and an alignment key 48, and a silicon oxide layer (not shown) is formed on the The surface of the fuse structure 46 and the alignment structure 48 . The bump pads 44 are electrically connected to the integrated circuit region, so after the subsequent packaging process is completed, the integrated circuit can be electrically connected to external circuits through the bump pads 44 . In addition, the fuse structure 46 is formed on the upper layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com