Semiconductor memory

A memory and semiconductor technology, applied in the field of dynamic RAM, can solve problems such as low data transmission rate, high chip cost, and small storage capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] Embodiments of the present invention are described below with reference to the drawings.

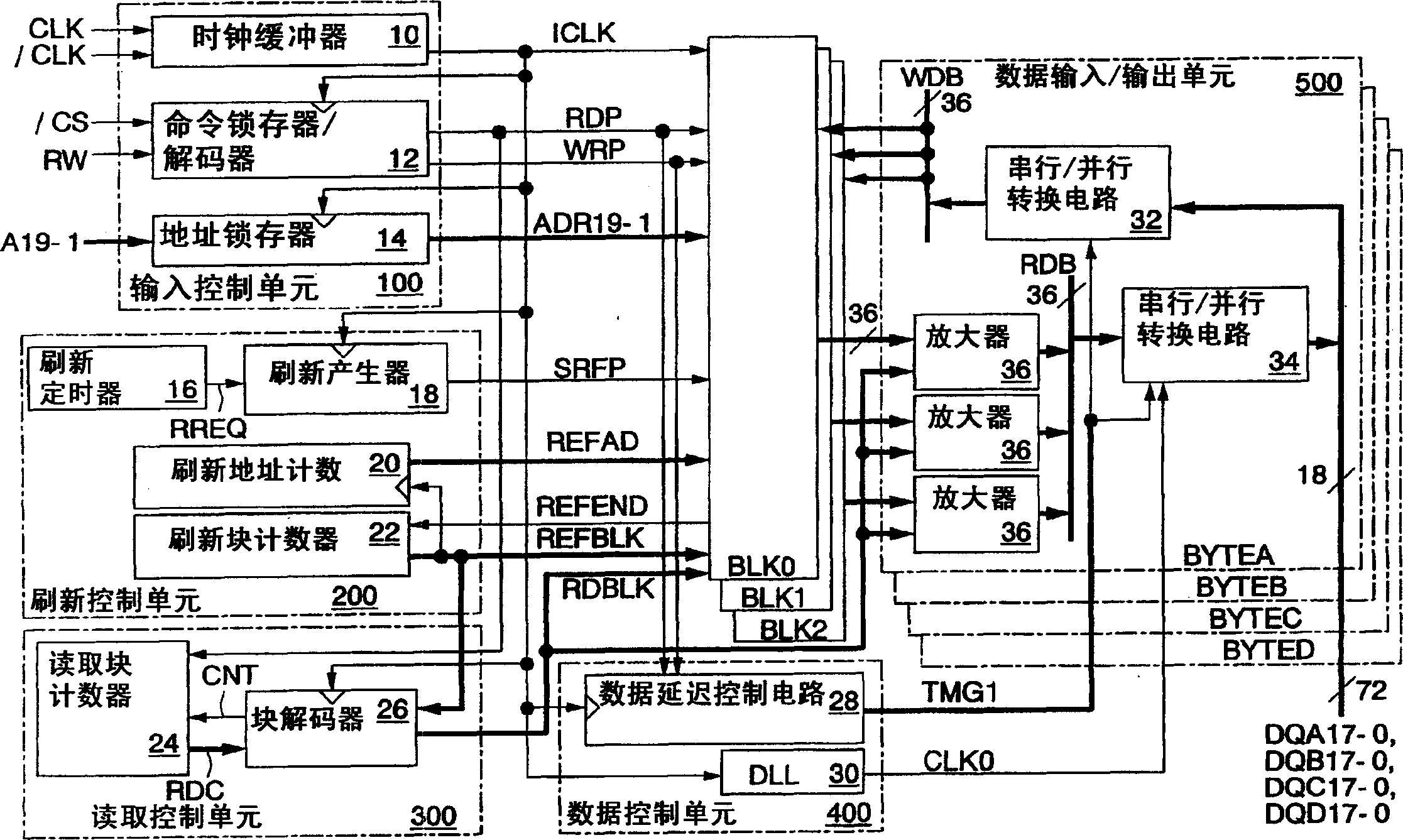

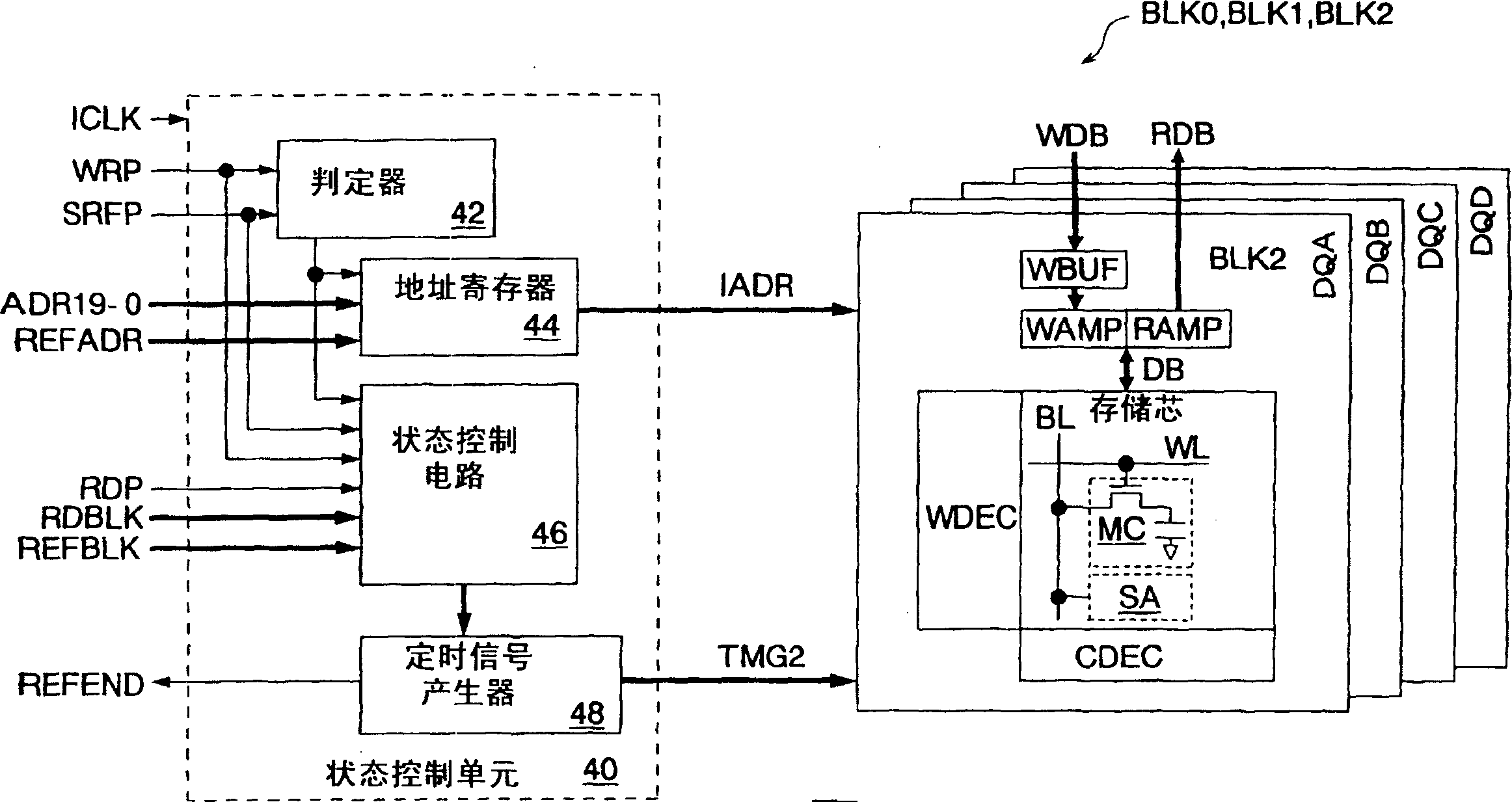

[0034] see figure 1 , which shows a first embodiment of a semiconductor memory according to the present invention. In this figure, each signal line indicated by a thick line is composed of a plurality of signal lines. Signals represented by a prefix with " / " represent negative logic.

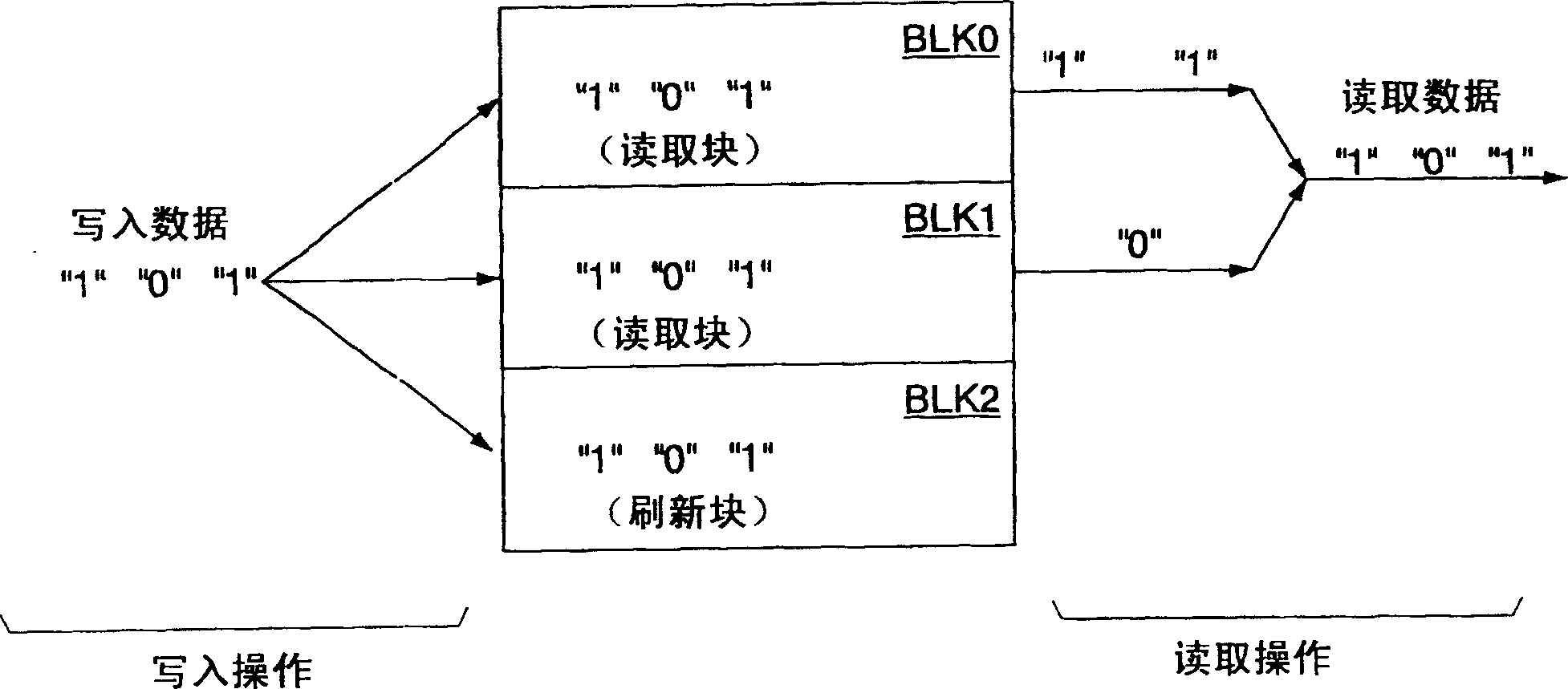

[0035] The semiconductor memory is formed as a clock-synchronized double data rate (DDR) pseudo-SRAM on a silicon substrate by using a CMOS process. DDR is an interface for inputting / outputting data in synchronization with rising and falling edges of a clock signal. The pseudo SRAM has an input control unit 100 , a refresh control unit 200 , a read control unit 300 , memory blocks BLK ( BLK0 - 2 ), a data control unit 400 and a data input / output unit 500 .

[0036] The pseudo SRAM also has input terminals for externally receiving clock signals CLK and / CLK, chip select signal / CS, read / write sig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com