Super junction device manufacturing method, super junction device, chip and circuit

A manufacturing method and super-junction technology, which is applied in semiconductor/solid-state device manufacturing, circuits, semiconductor devices, etc., can solve the problems that the uniformity of trench etching depth is difficult to control, and epitaxial filling is easy to form voids, etc., so as to improve epitaxial filling voids , Reduce the difficulty of trench etching, and reduce the effect of trench aspect ratio

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The specific implementations of the embodiments of the present invention will be described in detail below with reference to the accompanying drawings. It should be understood that the specific implementation manners described herein are only used to illustrate and explain the embodiments of the present invention, and are not used to limit the embodiments of the present invention.

[0030] It should be noted that the embodiments of the present invention and the features of the embodiments may be combined with each other under the condition of no conflict.

[0031] In the present invention, unless otherwise stated, the directional words used such as "upper, lower, top, bottom" are usually for the direction shown in the drawings or for the vertical, vertical or gravity direction The words used to describe the mutual positional relationship of the components mentioned above.

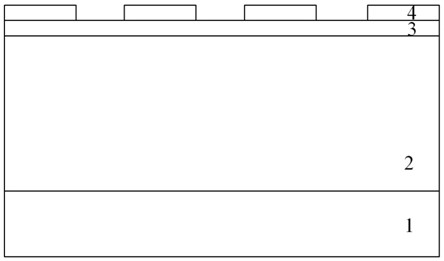

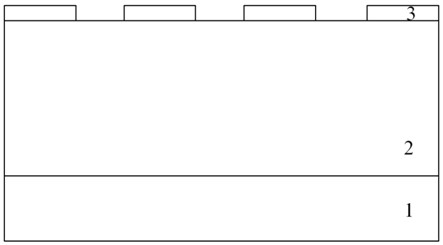

[0032] The present invention will be described in detail below with reference to the accompanyin...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap