Vertically-arranged MSM capacitor structure and manufacturing method thereof

A technology of capacitor structure and vertical layout, which is applied in the gold field to reduce costs and control risks, and overcome the effect of three-dimensional integration of capacitors that cannot be integrated

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

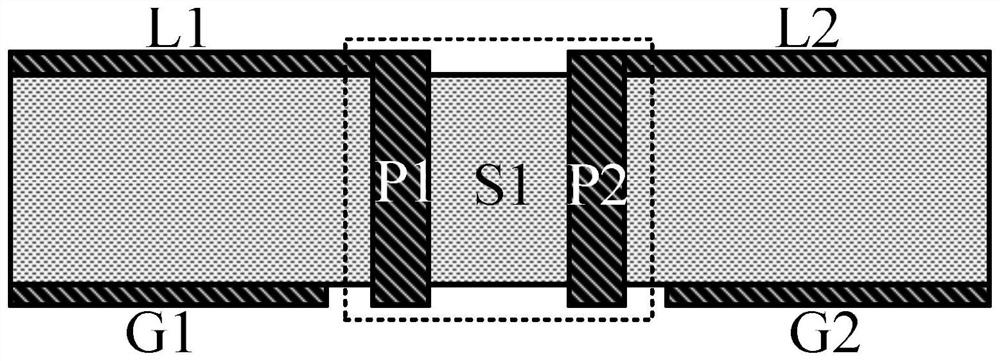

[0019] In the vertical MSM capacitor body structure, the two flat metallized through grooves, blind grooves or buried grooves are in a parallel relationship with each other. The sidewalls of the flat metallized through grooves, blind grooves or buried grooves can be metallized hollow structures or fully filled with metal. solid structure. The dielectric partition wall S1 can be a semiconductor dielectric layer sandwiched between two flat metallized through grooves, blind grooves or buried grooves and adjacent to the sidewalls. The semiconductor dielectric layer and the semiconductor dielectric substrate where it is located are of the same material and integrated Connect the capacitor terminal. L1 and L2 can be in the form of transmission lines such as microstrip line, stripline, coplanar waveguide, etc. The metal layers G1 and G2 that are not in communication with the capacitor plates can be used as ground or otherwise.

Embodiment 2

[0021] see image 3 . The difference between this embodiment and Embodiment 1 is that the two parallel grooves are buried grooves, that is, one end of the grooves does not extend to communicate with the metal layer. The difference between this embodiment and the process steps of Embodiment 1 is that the process step of performing a buried trench-to-through trench conversion using a backside chemical mechanical polishing CMP process can be omitted.

Embodiment 3

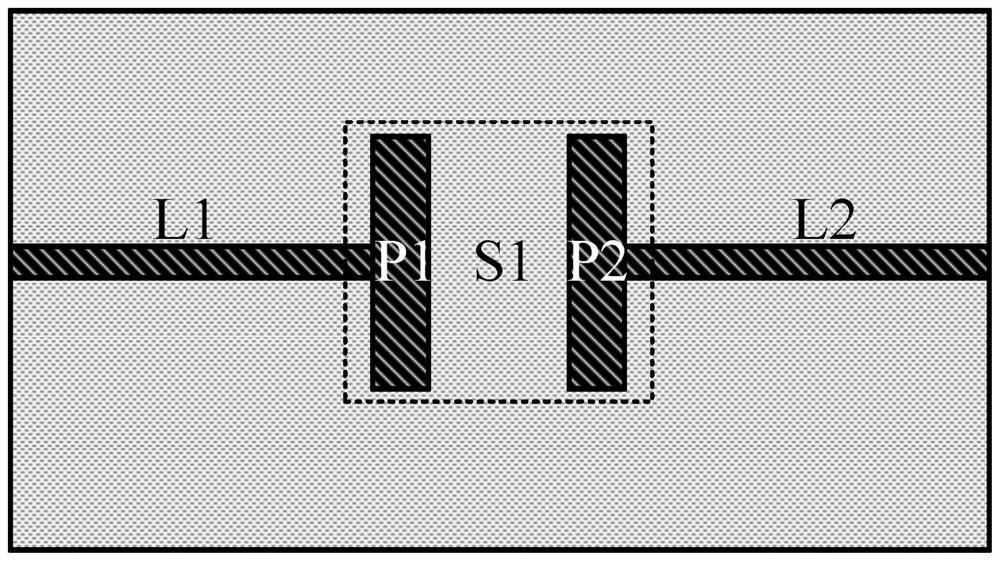

[0023] Figure 4 , Figure 5 It is a schematic front view of the vertical metal-semiconductor-metal MSM capacitor structure connected in series and parallel in an actual circuit, that is, as a demonstration of the actual layout usage of the capacitor structure. The series connection mode is characterized in that, as shown in Embodiment 1, the two capacitor lead-out ends are respectively connected to two parallel metal plate grooves, and the two lead-out ends can be located in the same metal layer, or can be located in different metal layers up and down. The grooves of the parallel metal plates are not connected. The parallel connection method is characterized in that the two capacitor lead-out ends are connected to one of the parallel metal plate grooves, the two lead-out ends can be located in the same metal layer, or can be located in different metal layers up and down, and the other parallel metal plate groove is connected to the ground end. This embodiment exemplifies t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com