High-voltage-resistant silicon carbide device and preparation method thereof

A high-voltage silicon carbide, silicon carbide technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of complex process, low reverse voltage, etc., to reduce on-resistance, on-resistance reduction, Effect of increasing channel mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

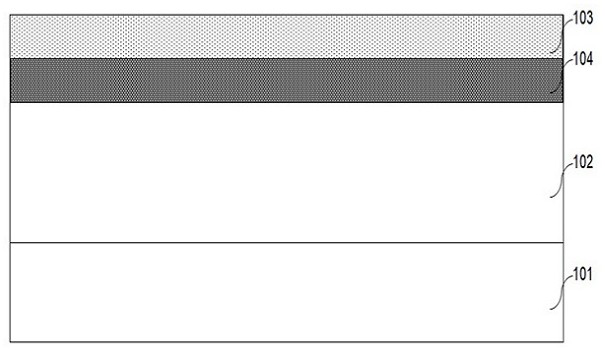

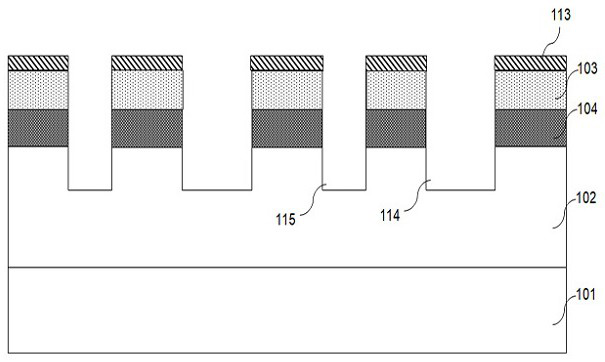

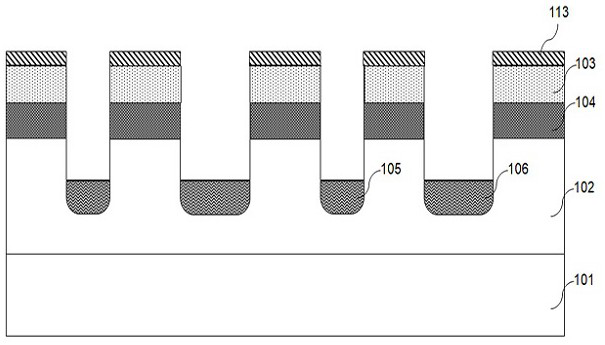

[0040] Such as Figure 1-5 As shown, taking the first conductivity type as N and the second conductivity type as P as an example, the preparation method of a high-voltage silicon carbide device of the present invention is as follows:

[0041] S1, epitaxial growth on the silicon carbide substrate 101 to form a silicon carbide epitaxial layer 102, specifically as figure 1 shown;

[0042] S2, forming a P-type blocking implantation region 104 on the silicon carbide epitaxial layer 102 by ion implantation of aluminum (Al) or boron (B), with a doping concentration of 5×10 15 cm -3 ~5×10 17 cm -3 , specifically as figure 1 shown;

[0043] S3, forming an N-type source implantation region 103 on the silicon carbide epitaxial layer 102 by implanting nitrogen (N) or phosphorus (P) ions, with a doping concentration of 5×10 16 cm -3 ~1×10 18 cm -3 , specifically as figure 1 shown;

[0044] S4, on the upper surface of the silicon carbide epitaxial layer 102, a patterned mask oxide...

Embodiment 2

[0053] The difference between this embodiment and Embodiment 1 is that the first conductivity type is P, and the second conductivity type is N. Specifically, the preparation method of the high-voltage silicon carbide device is as follows:

[0054] S1, epitaxial growth on the silicon carbide substrate 101 to form a silicon carbide epitaxial layer 102, specifically as figure 1 shown;

[0055] S2, forming an N-type blocking implantation region 104 on the silicon carbide epitaxial layer 102 by implanting nitrogen (N) or phosphorus (P) ions, with a doping concentration of 5×10 15 cm -3 ~5×10 17 cm -3 , specifically as figure 1 shown;

[0056] S3, forming a P-type source implantation region 103 on the silicon carbide epitaxial layer 102 by ion implantation of aluminum (Al) or boron (B), with a doping concentration of 5×10 16 cm -3 ~1×10 18 cm -3 , specifically as figure 1 shown;

[0057] S4, on the upper surface of the silicon carbide epitaxial layer 102, a patterned mask...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com