Area-friendly storage address mapping method for systolic array

A technique of pulsating arrays and storing addresses, applied in memory systems, instruments, electrical digital data processing, etc., can solve problems such as ratio reduction and complex address lines

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

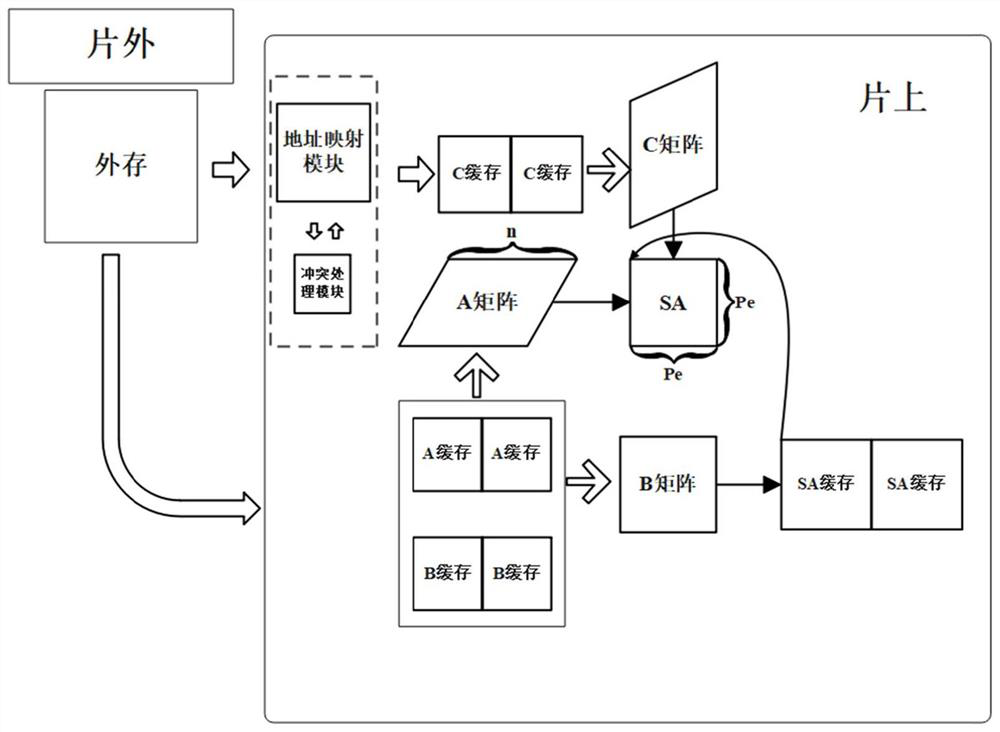

[0044] The purpose of the area-friendly storage address mapping method oriented to systolic arrays in the present invention is to optimize the on-chip area of the systolic accelerator, and to reduce the area cost of the on-chip memory as much as possible in terms of on-chip storage under the premise of ensuring operation efficiency and calculation accuracy. The area-friendly storage address mapping method oriented to systolic arrays of the present invention will be further described in detail below with reference to examples.

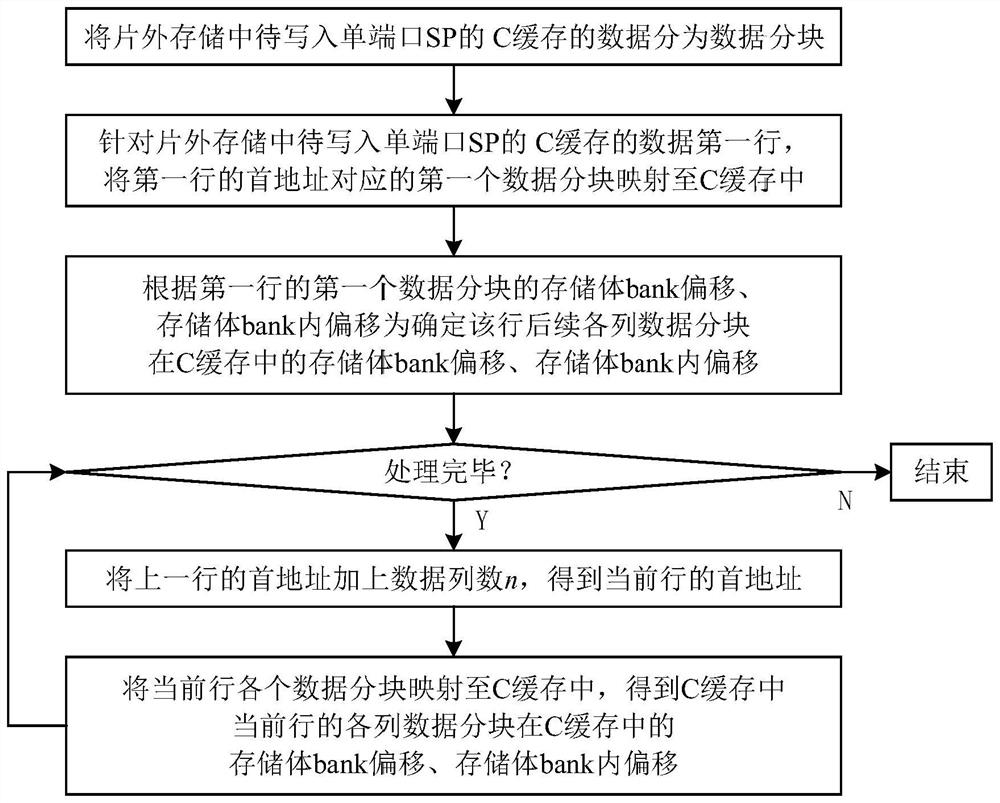

[0045] Such as figure 1 As shown, the area-friendly memory address mapping method for systolic arrays in this embodiment includes:

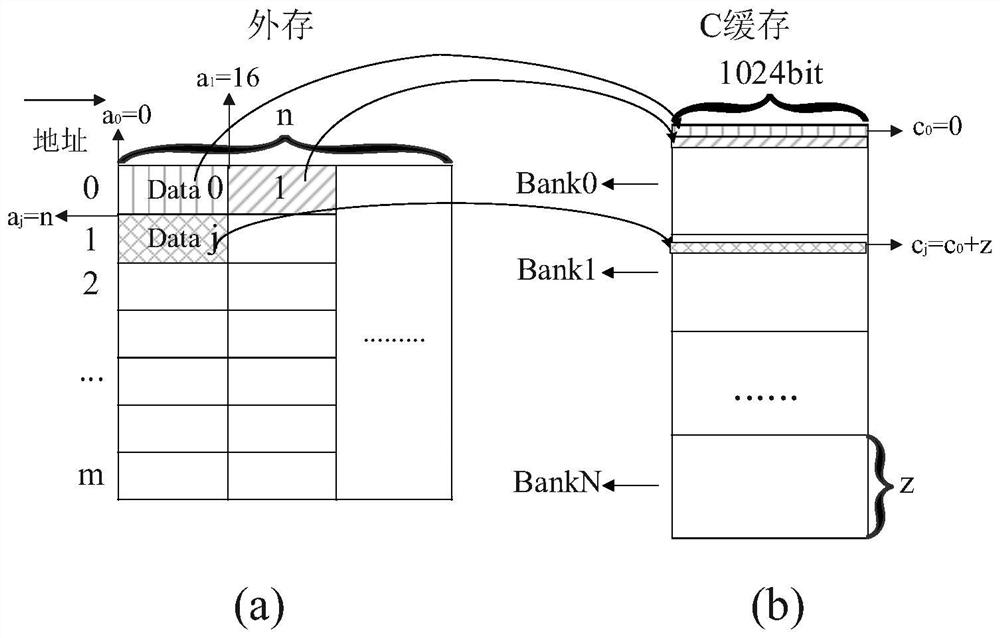

[0046] 1) The data to be written into the C cache of the single-port SP in the off-chip storage is divided into data blocks (block);

[0047] 2) For the first row of data to be written into the C cache of the single-port SP in the off-chip storage, set the first address a of the first row 0 The corresponding first dat...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap