Six-level assembly line CPU based on RISC-V instruction set

A RISC-V and instruction set technology, applied in concurrent instruction execution, instrumentation, computing, etc., can solve the problem of reduced CPU main frequency and instruction throughput, insufficient division of pipeline stages, low CPU main frequency and throughput, etc. problems, to achieve the effect of increased main frequency, easy control, and reduced execution time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0054] The pipeline IF stage circuit is attached figure 1 , consists of an instruction address generating module, an instruction fetching module, and a pc cache module. The working process of the IF level circuit is as follows: in the instruction address generation module, the current pc and the jump pc are added with 4 and then input to the data selector imux1, the pc_sel generation module generates the control signal pc_sel of imux1, and imux1 outputs the next instruction address to the PC counter . In the instruction fetch module, the selector imux2 selects the appropriate address as the input of the ITCM address terminal, and the ITCM outputs instructions according to the input address. The PC buffer can also be used as an inter-segment register between the IF stage and the FD stage, and outputs the PC value of the IF stage to the next stage of the FD stage.

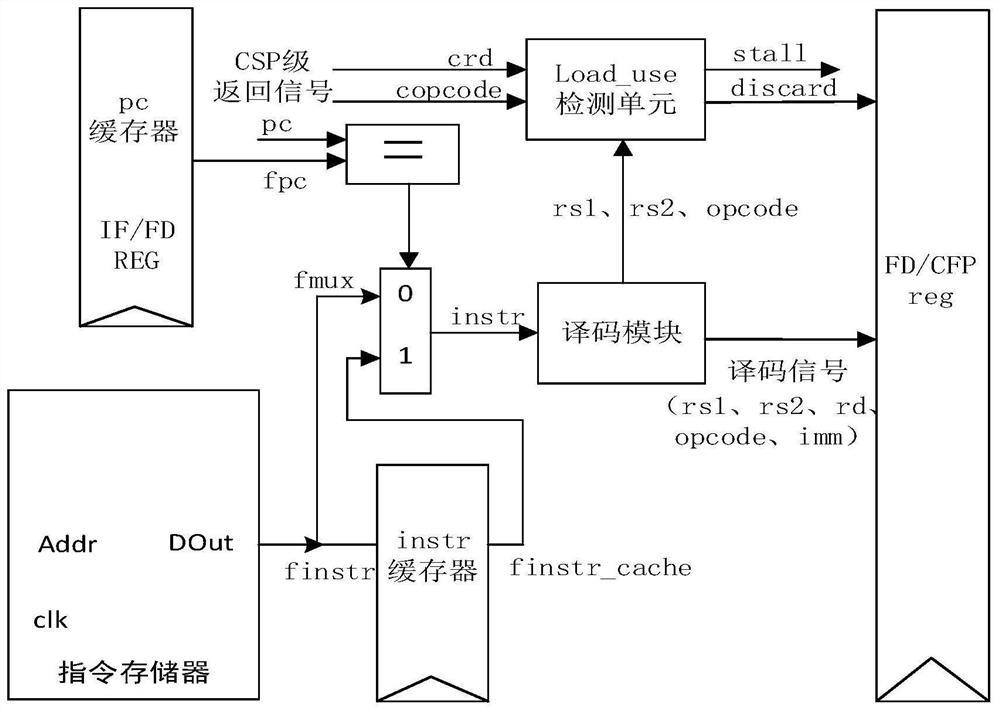

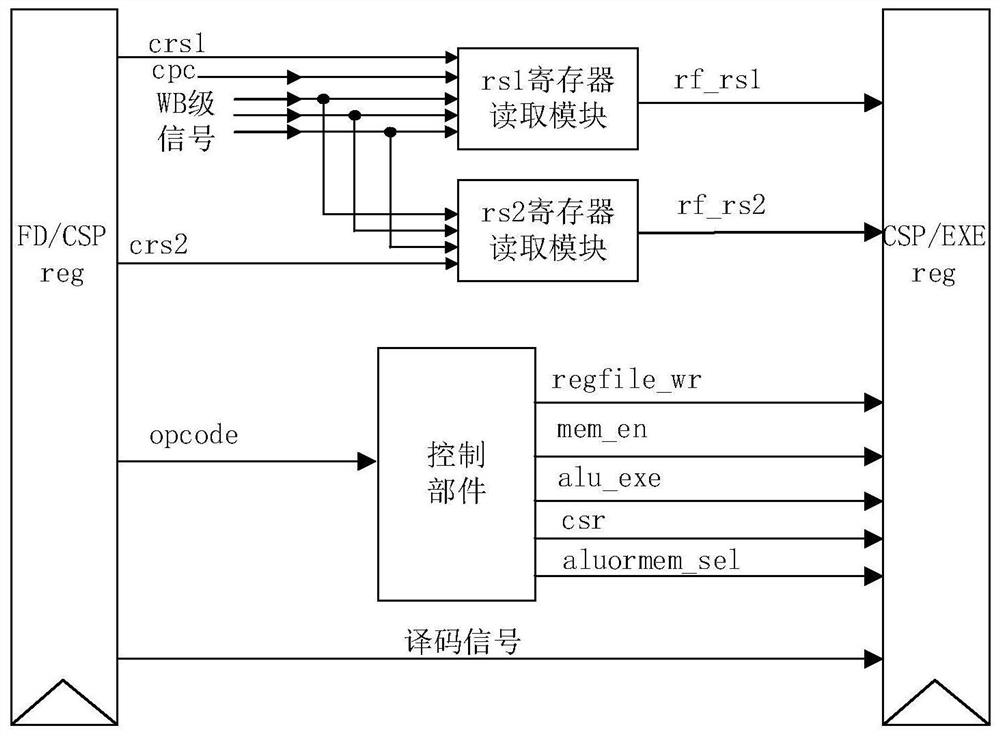

[0055] The pipeline FD level circuit is attached figure 2 , consists of a load_use detection unit, an instruct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com