Method for improving memory logic calculation efficiency based on memristor

A logic computing and memristor technology, applied in the field of improving the efficiency of memristor-based in-memory logic computing, to achieve the effects of improving efficiency, reducing computing delay, and improving service life

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

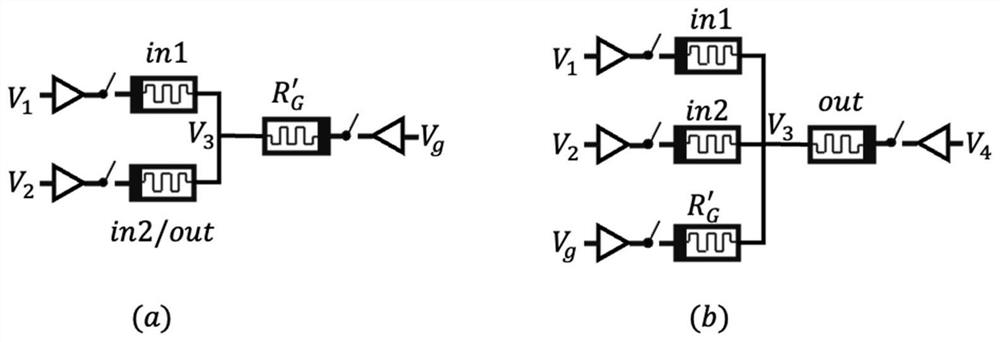

[0041] combine figure 1 , this embodiment discloses a method for improving the logic calculation efficiency in the memristor memory, and the specific steps are as follows:

[0042]Step 1. The resistors required by the gates of the IMPLY logic family increase the hardware overhead of the circuit and increase the complexity of the memristor row / column decoder. According to this feature, it is proposed to use a memristor instead of a resistor.

[0043] figure 2 (a) shows the improved IMPLY logic family gate, which uses a memristor R′ G to replace the resistor. The input memristors in1 and in2 are respectively connected to the voltage source V 1 and V 2 , the memristor R′ G Connect the voltage source V g . Suppose in1, in2 and R' G The voltage of the contributing node is V 3 , then according to Kirchhoff’s current law, we have:

[0044]

[0045] where R in1 and R in2 are the resistance values of the input memristors in1 and in2, respectively. For a memristor no...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com