Chip test method and system and readable storage medium

A chip testing and chip technology, applied in the field of testing, can solve problems such as difficulty in compatibility, time-consuming test and verification, increased workload, time-consuming and energy-consuming problems, and achieve the effect of improving production efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

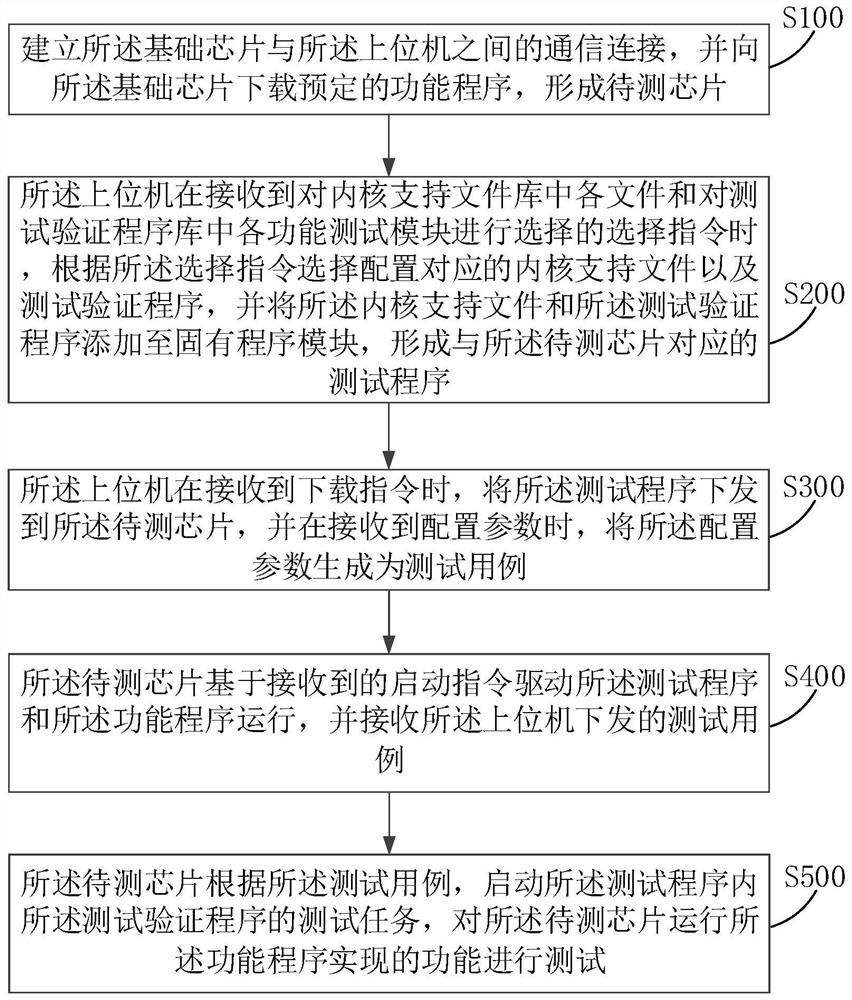

[0045] It should be noted that the use of step numbers (letters or numbers) in the present invention to refer to some specific method steps is only for the purpose of convenience and brevity in description, rather than limiting these method steps with letters or numbers order of. Those skilled in the art can understand that the sequence of relevant method steps should be determined by the technology itself and should not be unduly limited due to the existence of step numbers.

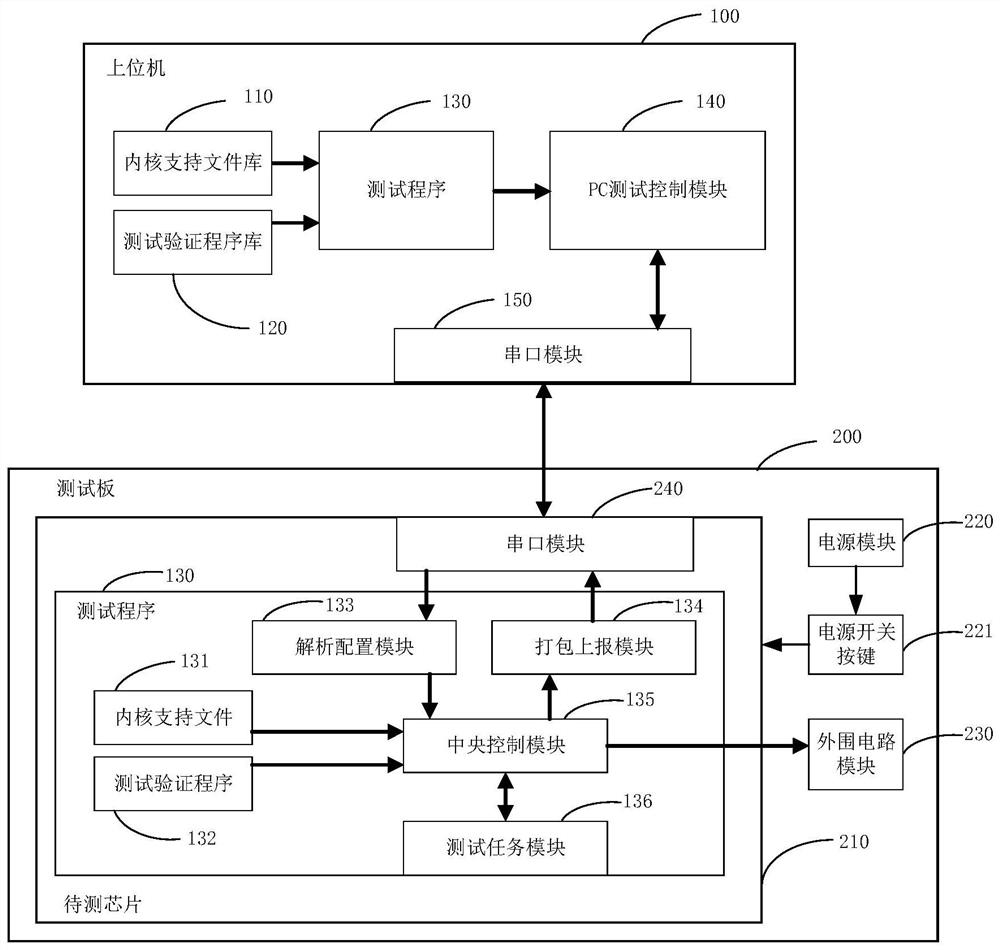

[0046] Please refer to figure 1 , figure 1 It is a schematic structural diagram of a chip testing system applied to the chip testing method of the present invention. The test system includes a host computer 100 and a test board 200 , the test board 200 is equipped with a basic chip, and the basic chip is connected to the host computer 100 by communication. Wherein, the basic chip can be a CPLD (Complex Programming logic device, complex programmable logic device) chip, or an FPGA (Field Programmable G...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com