Power module thermal modeling method based on Fourier series

A Fourier series and power module technology, which is applied in the field of thermal modeling of power modules based on Fourier series, can solve the problems of limited application, limited versatility, and unexpanded multi-layer packaging structure of power modules. The solution time is short, there is no convergence problem, and the calculation amount is small.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

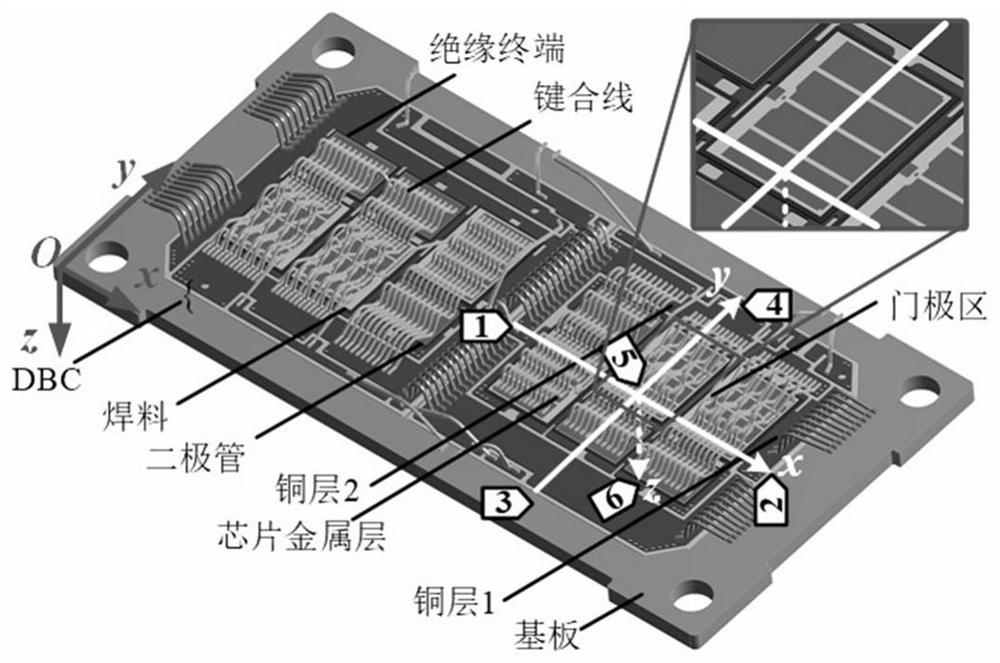

[0083] In order to explain the present invention in more detail, the present invention will be further described in detail below in conjunction with the accompanying drawings, taking the SEMiKron power semiconductor module SEMiX603GB12E4p as an example.

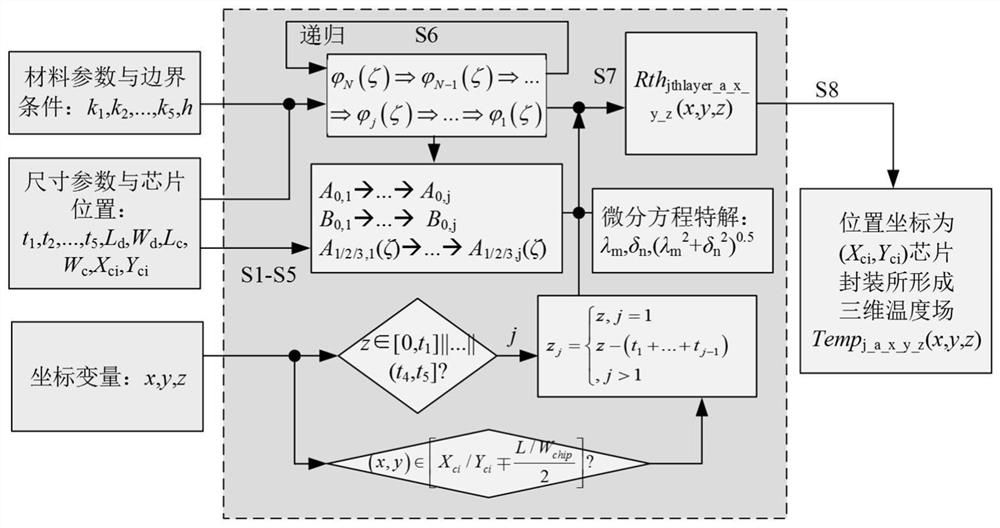

[0084] The power module thermal modeling method based on Fourier series proposed by the present invention, the specific steps include:

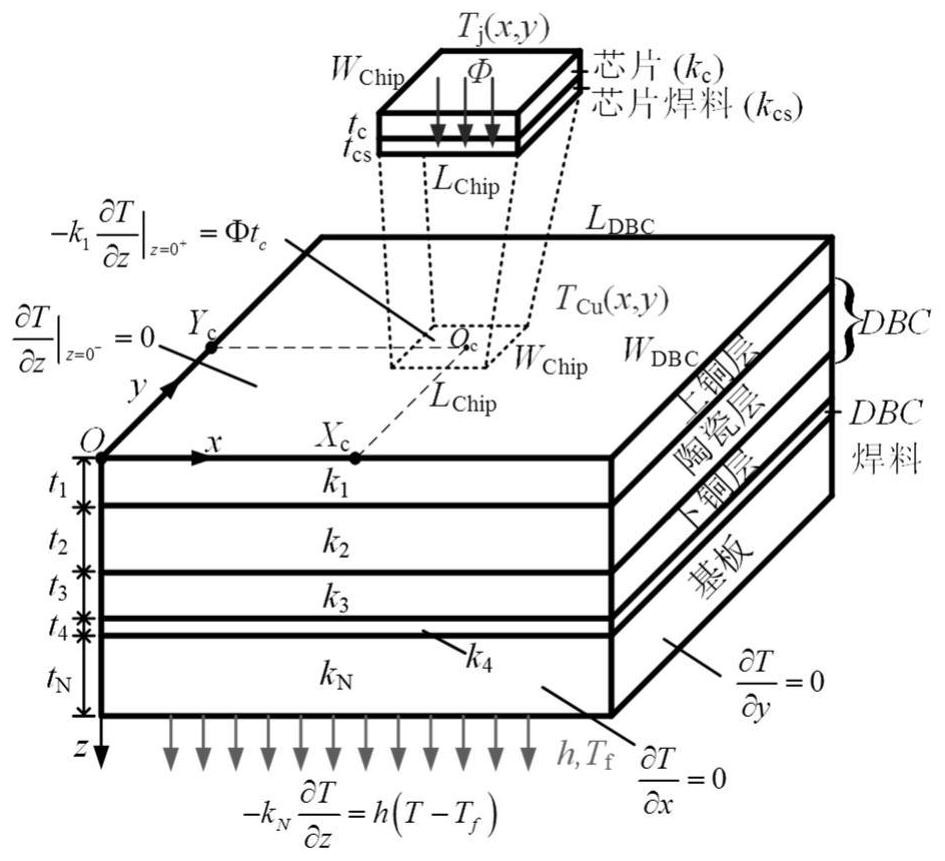

[0085] S1. Establish a three-dimensional Cartesian coordinate system, and write the Laplace three-dimensional heat conduction partial differential equation about the temperature of the power module;

[0086] S2. Determine the boundary condition expression on the bottom surface of the module according to the heat dissipation method of the module; determine the boundary condition expression on the top surface of the module according to the power loss of the chip; determine the boundary condition expression on the side of the module according to the thermal insulation characteristics of the side...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com