Si-GeSn-Si heterogeneous GeSn-based solid-state plasma PiN diode and preparation method thereof

A plasma and diode technology, used in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems affecting the integration performance and stealth performance of antenna systems, the carrier injection ratio of the device is not high, and PiN diode application limitations and other issues to achieve the effect of improving integration and stealth performance, improving antenna performance, and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

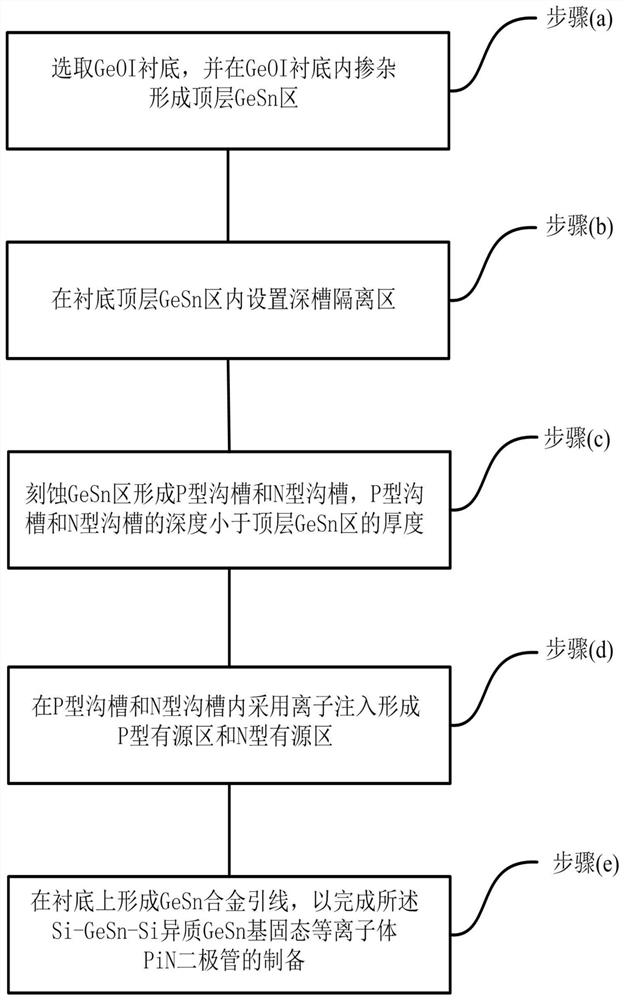

[0060] See figure 1 , figure 1 It is a flow chart of a method for manufacturing a Si-GeSn-Si heterogeneous GeSn-based solid-state plasma PiN diode according to an embodiment of the present invention, the method is suitable for preparing a lateral solid-state plasma PiN diode based on a GeOI substrate, and the Si-GeSn -Si heterogeneous GeSn-based solid-state plasmonic PiN diodes are mainly used to make silicon-based highly integrated antennas. The method comprises the steps of:

[0061] (a) select a GeOI substrate, and dope in the GeOI substrate to form a top GeSn region;

[0062] (b) setting a deep trench isolation region in the GeSn region on the top layer of the substrate;

[0063] (c) etching the GeSn region to form a P-type trench and an N-type trench, and the depth of the P-type trench and the N-type trench is less than the thickness of the top-layer GeSn region;

[0064] (d) forming a P-type active region and an N-type active region by ion implantation in the P-type ...

Embodiment 2

[0104] See Figure 2a-Figure 2t , Figure 2a-Figure 2t It is a schematic diagram of a preparation method of a Si-GeSn-Si heterogeneous GeSn-based solid-state plasma PiN diode according to an embodiment of the present invention. A Si-GeSn-Si heterogeneous GeSn-based solid-state plasma PiN diode between 50 microns and 150 microns) can be used as an example to describe in detail, and the specific steps are as follows:

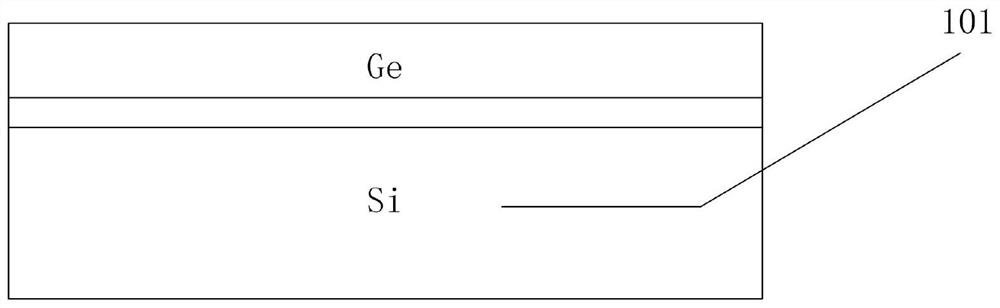

[0105] S10, selecting a GeOI substrate.

[0106] See Figure 2a , the crystal orientation of the GeOI substrate 101 may be (100) or (110) or (111), without any limitation here. In addition, the doping type of the GeOI substrate 101 can be n-type or p-type, and the doping concentration is, for example, 0.5×10 14 ~1×10 15 cm -3 , the thickness of the top layer Ge is, for example, 30-120 μm.

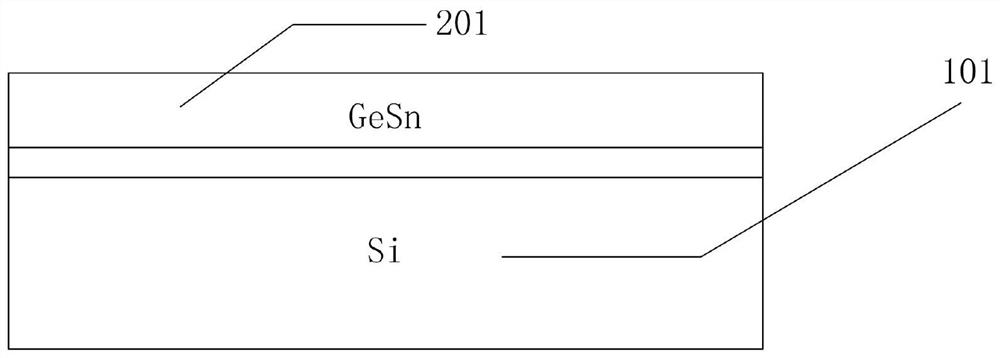

[0107] S20, doping in the GeOI substrate to form a top-layer GeSn region.

[0108] See Figure 2b The specific method may be: photoetching the GeOI substrate, doping t...

Embodiment 3

[0148] Please refer to image 3 , image 3 It is a schematic diagram of the device structure of the Si-GeSn-Si heterogeneous GeSn-based solid-state plasma PiN diode according to the embodiment of the present invention. The Si-GeSn-Si heterogeneous GeSn-based PiN diode adopts the above-mentioned figure 1 The preparation method shown is made, specifically, the Si-GeSn-Si heterogeneous GeSn-based solid-state plasma PiN diode is prepared and formed on the GeOI substrate 301, and the P region 303, the N region 304 of the diode and the lateral position of the P The intrinsic region between region 303 and the N region 304 is located in the top GeSn layer 302 of the substrate. Wherein, the PiN diode adopts deep trench isolation technology, that is, a deep trench isolation region 307 is provided outside the P region 303 and the N region 304, and the depth of the isolation trench 307 is greater than or equal to the thickness of the top GeSn layer 302. In addition, the P region 303 an...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com