Interface system for interconnecting bare core and MPU and communication method thereof

A communication method and technology of an interface system, which are applied in the field of interface systems for interconnecting bare cores and MPUs, can solve problems such as difficulty in use, poor versatility, and complex technical systems, and achieve the effect of reducing complexity and small amount of data.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

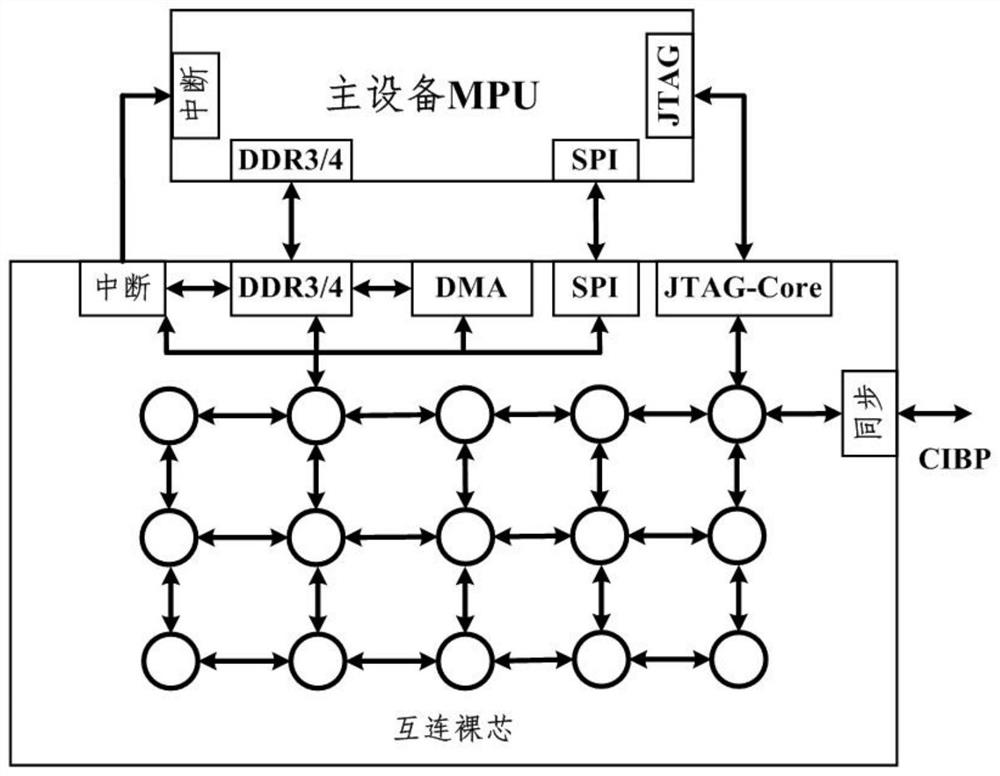

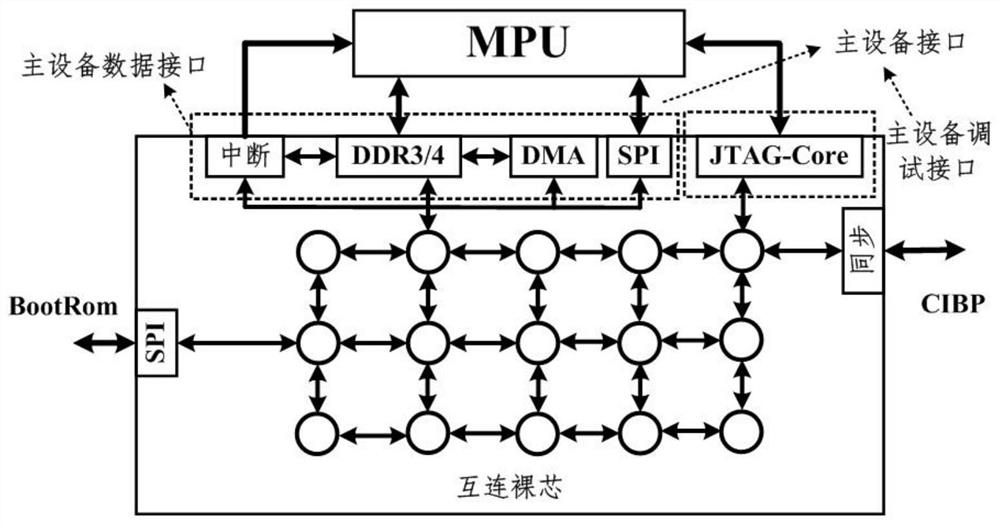

[0041] Such as figure 1 with figure 2 As shown, the interface system of interconnecting the bare core and the MPU includes: a data interface, an interrupt interface and a debugging interface; Self-starting, the DMA control interface is used for DMA start and end control; the interrupt interface is used to receive the interrupt data packet from the network and analyze the pulse interrupt input required by the MPU, and the interrupt interface receives the interrupt address operation from the data interface at the same time And it is converted into an interrupt event and sent; the debug interface includes a JTAG-Core debug interface, which is used to receive a debug packet from the network and translate it into a JTAG protocol for MPU debugging.

[0042] The SPI interface, DDR data interface, DMA control interface and interrupt interface are connected to the same router in the interconnected bare core; the debugging interface is connected to another router in the interconnected...

Embodiment 2

[0052] The communication method between the interconnected bare core and the MPU, data transmission is performed between the interconnected bare core and the MPU through a data interface, interrupt transmission is performed through an interrupt interface, and MPU debugging is performed through a debugging interface; the MPU controls two or two MPUs through a DMA control interface The data access between the above slave devices is controlled; the data interface includes an SPI interface, a DDR data interface and a DMA control interface; the debugging interface includes a JTAG-Core debugging interface.

[0053] The MPU sends a memory access request to the interconnected bare core in the DDR data format through the data interface; the interconnected bare core converts the response data packet into the DDR data format and sends it to the MPU.

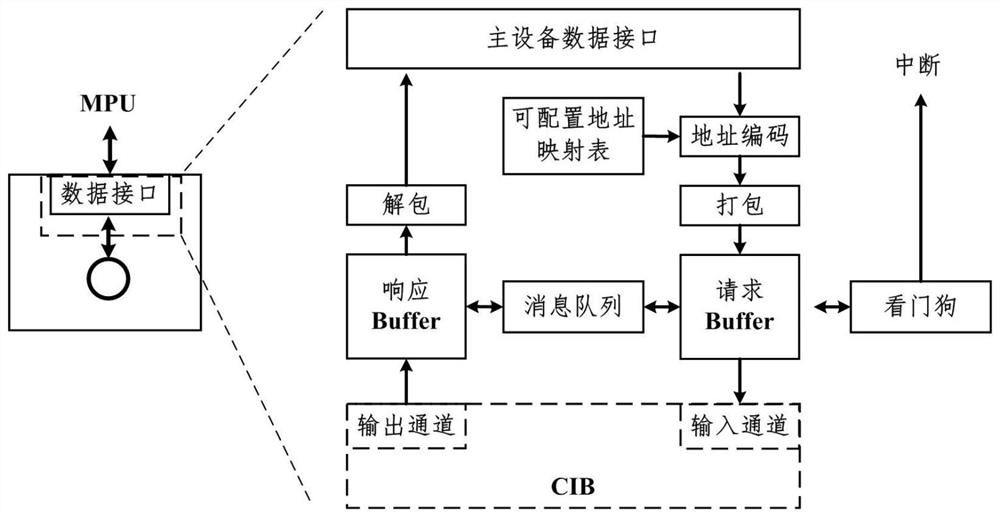

[0054] When the MPU sends a request event to the interconnected bare core, a request packet is generated, and the generation of the request...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com