Chip design optimization system and method based on dynamic unbalanced clock

A technology of chip design and optimization methods, applied in computer-aided design, computing, special data processing applications, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The chip design optimization system and method based on the dynamic unbalanced clock of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

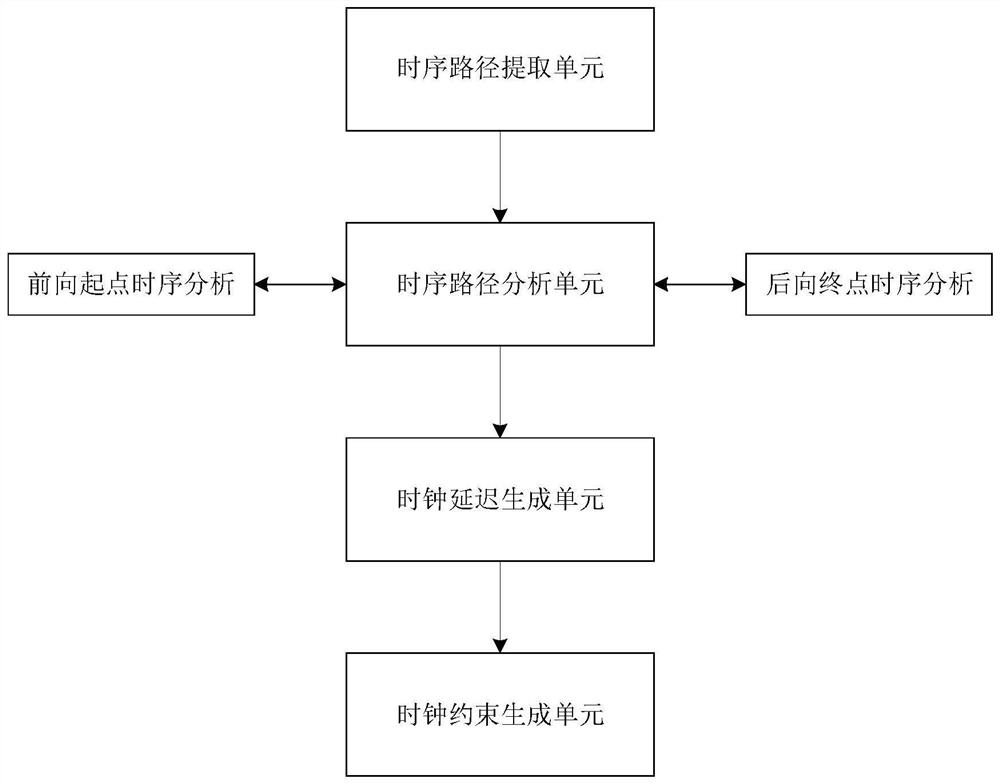

[0045] Such as figure 1 As shown, a chip design optimization system based on a dynamic unbalanced clock includes sequentially connected timing path extraction unit, timing path analysis unit, clock delay generation unit and clock constraint generation unit.

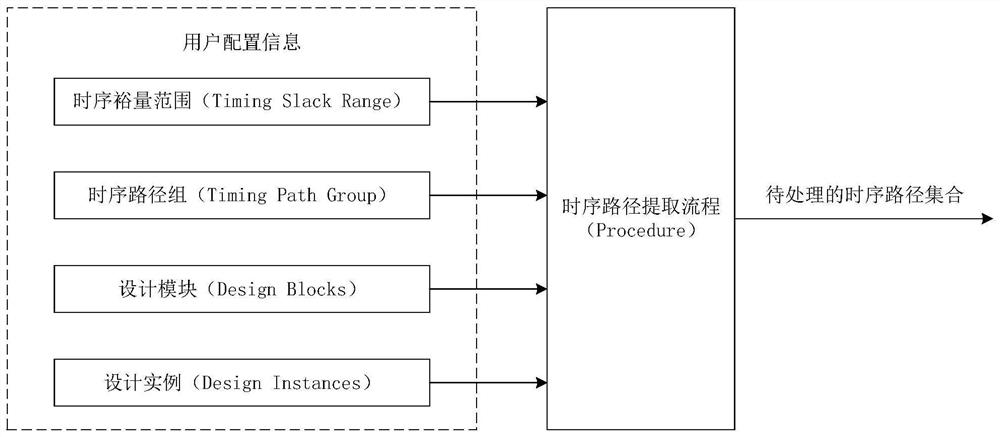

[0046] The timing path extracting unit is used to extract the timing paths to be analyzed that meet the requirements from the designed timing paths, and send them to the timing path analysis unit.

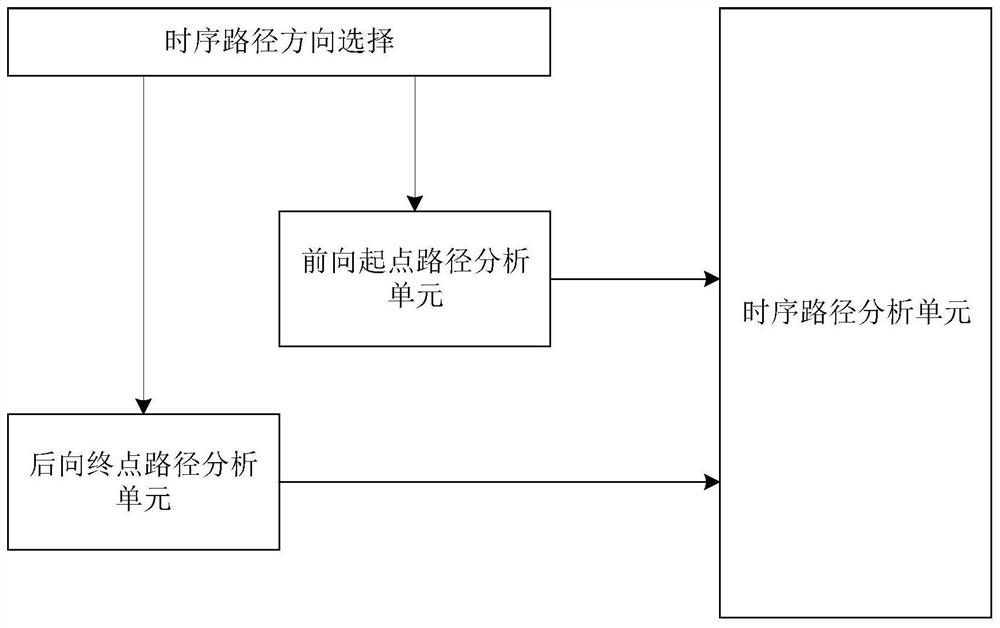

[0047] combine image 3 , the timing path analysis unit includes a forward start timing analysis unit and a backward end timing analysis unit, the forward start timing analysis unit is used to analyze and extract the timing state when the starting point of the timing path is taken as the end point...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com