IC die to IC die interconnection using error correcting code and data path interleaving

A technology for encoding data and decoding data, which is applied in electrical digital data processing, transmission link error control systems, circuits, etc., and can solve problems such as high silicon area cost, extra energy consumption, and increased heat generation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] It should be understood at the outset that, although an illustrative implementation of one or more embodiments is provided below, the disclosed systems and / or methods may be implemented using any number of techniques, whether currently known or in existence. The invention should in no way be limited to the illustrative implementations, drawings, and techniques illustrated below, including the exemplary designs and implementations illustrated and described herein, but rather be within the scope of the appended claims and their equivalents Modified within the full range of .

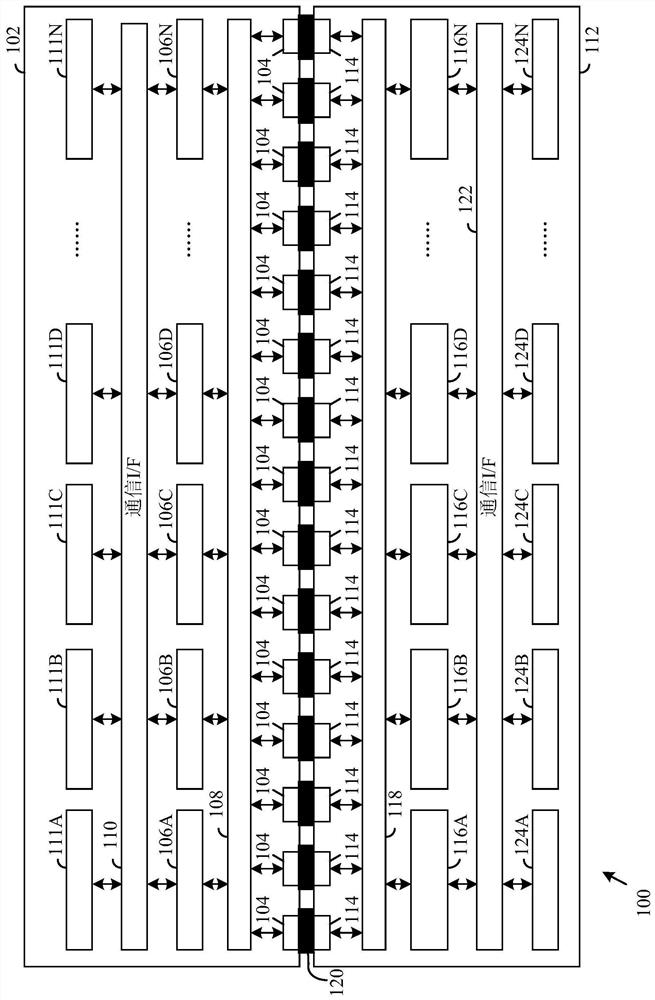

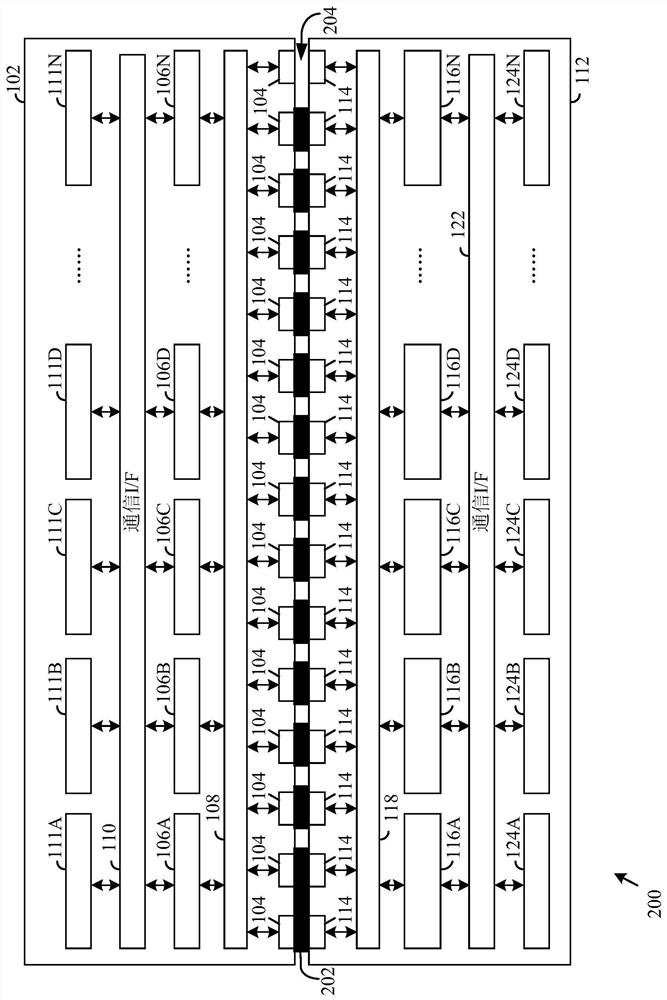

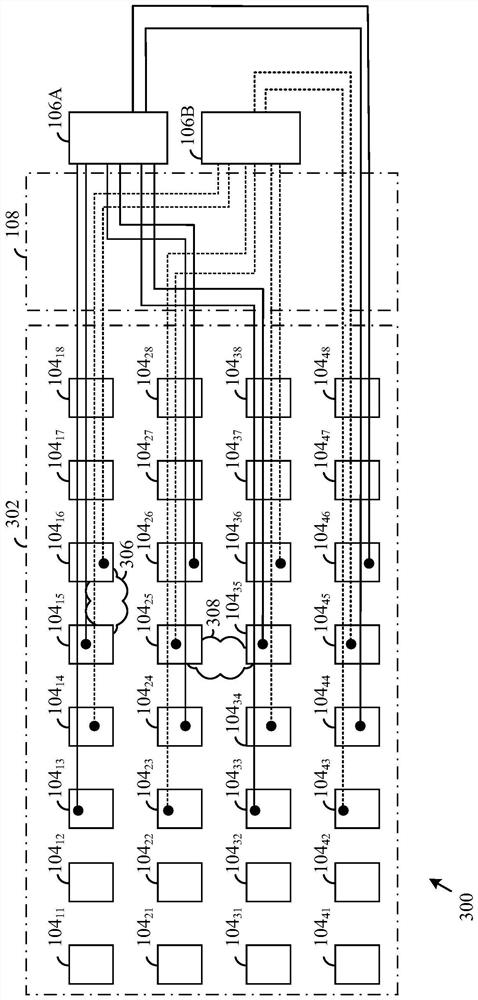

[0033] figure 1 is a cross-sectional side view illustrating a portion of a multi-chip module having a first integrated circuit (IC) die 102 and a second IC die 112 constructed in accordance with the described embodiments. The first IC die 102 includes a plurality of processing systems 111A- 111N coupled to each other through a communication interface 110 . Communication I / F 110 may be a NoC (or pa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com