Memory error correction method, memory controller and electronic equipment

A memory controller and memory error correction technology, applied in the field of memory, can solve problems such as inability to correct and obtain correct data, inability to meet the requirements of memory reliability, and limited error correction capability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

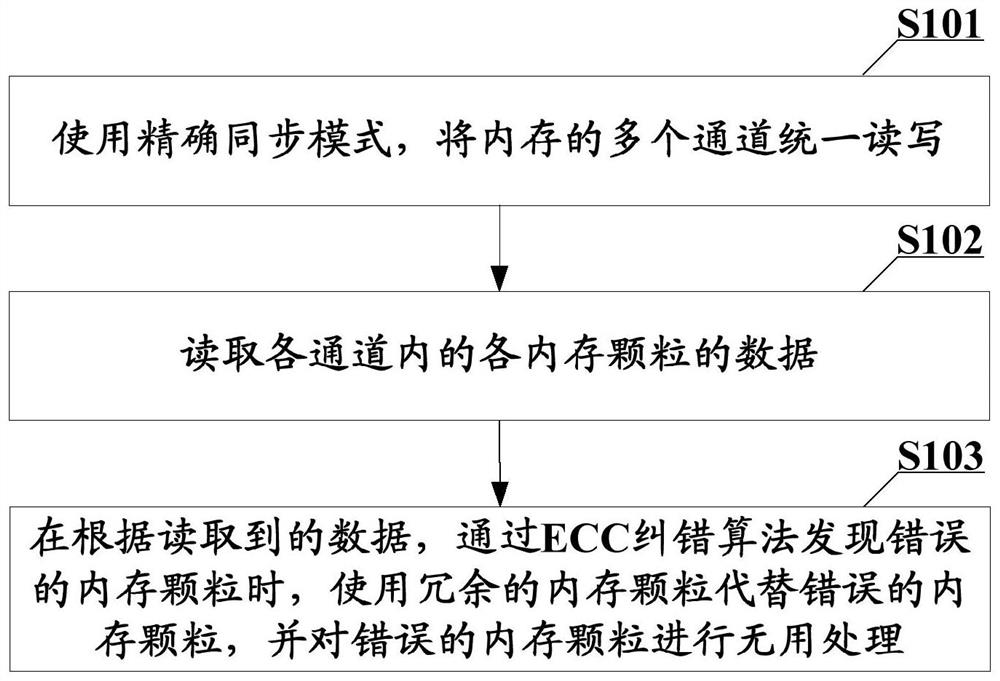

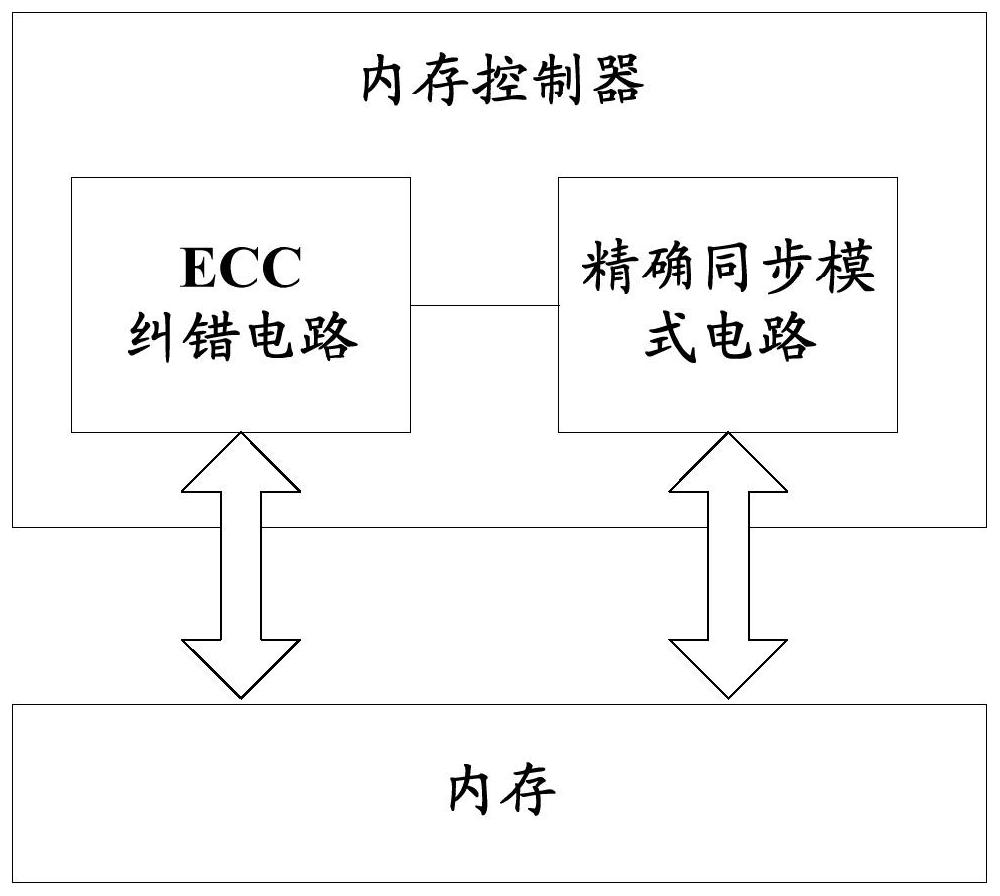

[0036] The embodiment of this application provides a memory error correction method, which can be found in figure 1 shown, including:

[0037] S101: Use the precise synchronization mode to uniformly read and write multiple channels of the memory.

[0038] It should be noted that the so-called precise synchronization mode is also called Lockstep lockstep mode (LockStep ChannelMode), which uses the same, redundant hardware components to process the same instruction at the same time, so that a CPU cache line (Cache -line) is distributed over several memory channels.

[0039] After using the precise synchronization mode, multiple channels of memory can be used to store data on the same CPU cache line, making it possible to share memory particles among multiple channels.

[0040] S102: Read data of each memory particle in each channel.

[0041] It should be noted that, in the embodiment of the present application, the read data should meet the minimum data requirements of the EC...

Embodiment 2

[0081] In this embodiment, a specific memory error correction process applied to a DDR5 memory is taken as an example to illustrate this application.

[0082] Use the precise synchronization mode to uniformly address the DDR5 memory, read and write the two channels (channel 0 and channel 1) uniformly, and distribute the data on the two channels.

[0083] The ECC error correction algorithm uses the RS (144, 128) algorithm, and the ECC word is 128+16bit.

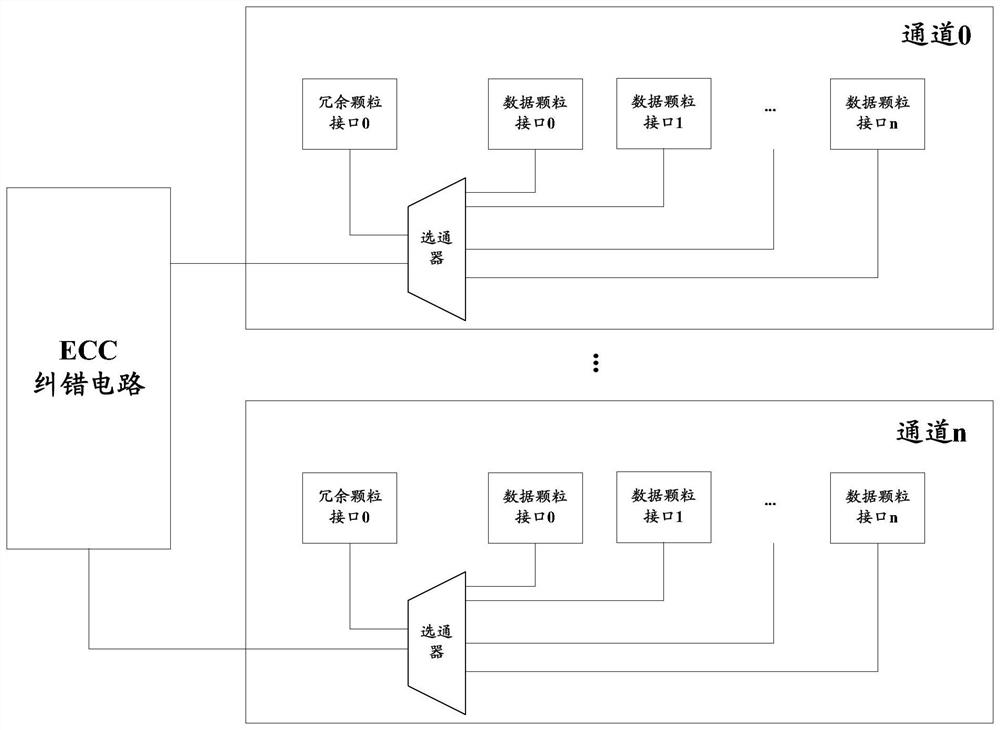

[0084] Since the data bit width of DDR5 memory is 32+8bit. The 2 channels are read twice and have 128+32bit. The ECC error correction algorithm only uses 16 bits of 32 bits redundant data. In this way, 16bit redundant data is left for the two channels. Each channel has 8 bits of redundant data left. That is to say, each channel has one redundant memory particle.

[0085] In the initial state, such as Image 6 As shown, the two channels consist of D0, D1, D2, D3, D4, D5, D6, D7, C0, a total of 18 memory particles with a s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com